## Aware Systems on Chip

Axel Jantsch

January 14, 2016

# Making Chips Aware

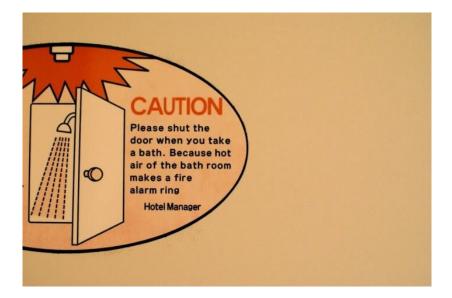

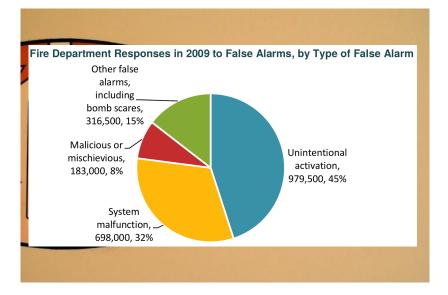

#### **False Alarms**

### **False Alarms**

# Air France Flight 447 in 2009

# Air France Flight 447 in 2009

The BEA's final report from 2012 concluded that:

> "Temporary inconsistency between the measured airspeeds, likely following the obstruction of the Pitot probes by ice crystals"

caused the autopilot to disconnect, after which the crew reacted incorrectly and ultimately led the aircraft to an aerodynamic stall from which they did not recover.

Nature does nothing uselessly, Aristotle

Does a bridge know when it is weakening?

Is a thermometer aware of the temperature?

Does a robot recognize its own limps?

Does a surveillance system recognize its own camera?

Is a human aware of her immune system?

Is a human aware of her own arms?

### Which Ingredients Lead to Awareness ?

Johan Moreelses "Der Alchemist", 1630

## Which Ingredients Lead to Awareness ?

Johan Moreelses "Der Alchemist", 1630

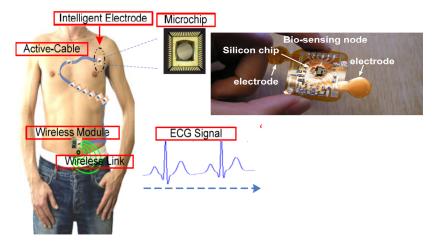

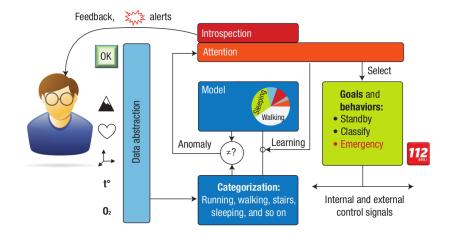

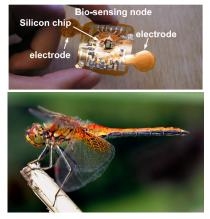

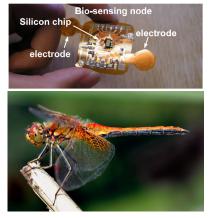

# Awareness for Resource Constrained, Insect-like Gadgets

courtesy of KTH

### Abstractions and Models

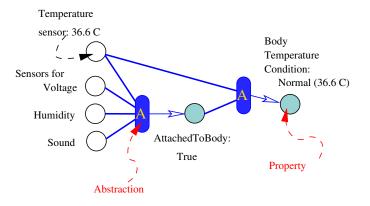

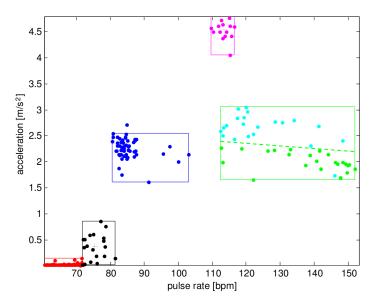

#### Abstraction: Mapping of Measurements $\Rightarrow$ Properties

### Abstractions and Models

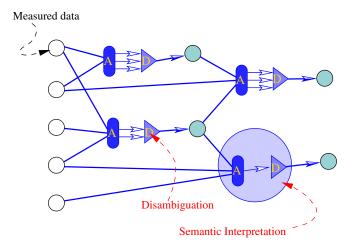

# Disambiguation

#### Selection among several interpretations

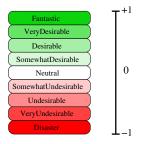

# **Desirability Scale**

#### Desirability is the common, internal currency.

Semantic Attribution maps the values of a property to a point in the desirability scale.

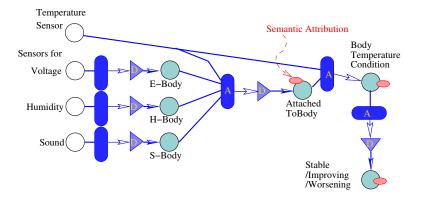

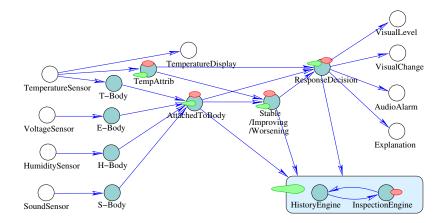

## **BioPatch with Semantic Attribution**

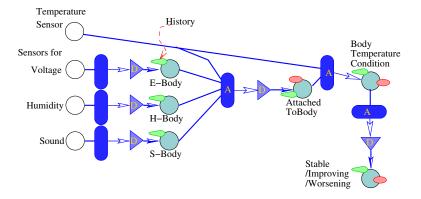

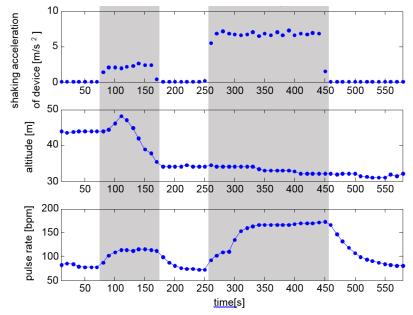

## History

History of a Property The evolution of the values of a property.

Abstracted History The history stores abstracted values.

Attributed History The history is annotated with attributions.

Fading History If the property values are more abstracted the longer ago they have occurred.

Consolidating History Relevant memories are enforced, irrelevant memories are cleaned.

Evolving History Memories are adjusted to fit later observations.

# **BioPatch with History**

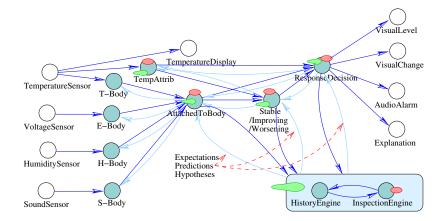

# **Expectations and Goals**

- Expectations on Environment

- Expectations on Subject

- Sub-Goals

- Goals

- Purpose

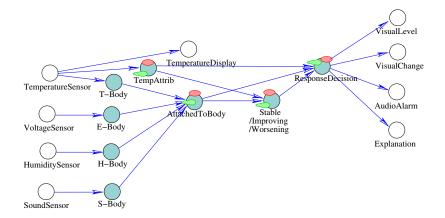

# Acting BioPatch

## Inspection and Simulation

#### Self Inspection Engine

#### Model Transformation

Simulation

Ernst Mach "Innenperspektive", 1886

## Self-inspecting BioPatch

# **BioPatch with Top-down Prediction**

# Health Monitoring

# Health Monitoring

# Health Monitoring

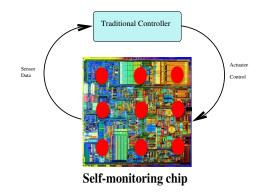

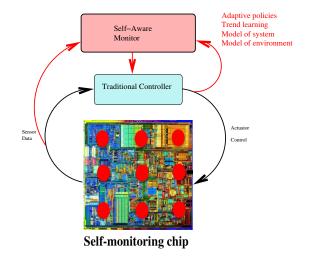

#### Self-monitoring chip

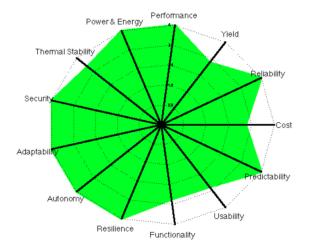

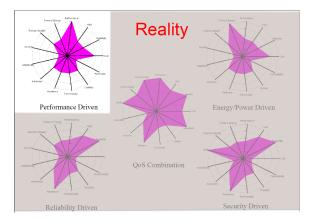

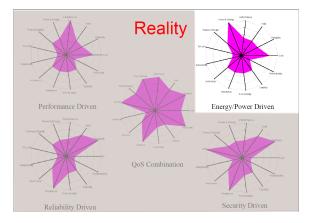

# The SoC Radar

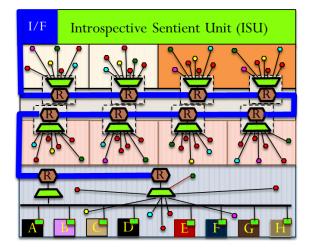

### CPSoC - A Sensor Rich SoC Platform

#### CPSoC - A Sensor Rich SoC Platform

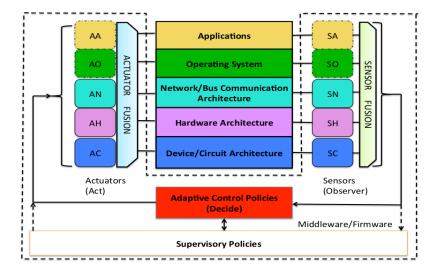

### Sensing and Actuating at All Layers

| Layers                   | Virtual/Physical Sensors                                                   | Virtual/Physical Actuators                                                         |

|--------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Application              | Workload, Power, Energy,<br>Execution Time                                 | Approximation,<br>Algorithmic choice,<br>Transformations                           |

| Operating<br>System      | System utilization,<br>Peripheral states                                   | Task allocation,<br>Partitioning, Scheduling,<br>Migration, Duty cycle             |

| Network/Bus              | Bandwidth, Packet/flit<br>status, Channel status,<br>Congestion            | Adaptive routing,<br>Dynamic BW allocation,<br>Channel allocation, Flow<br>control |

| Hardware<br>Architecture | Cache miss rate, Access<br>rate, IPC, Throughput,<br>Resource utilization  | Cache sizing, Issue width sizing, Reconfiguration, Resource provisioning           |

| Circuit/Device           | Circuit delay, Aging<br>effects, Leakage,<br>Temperature, Device<br>faults | DVFS, Clock gating,<br>Power gating                                                |

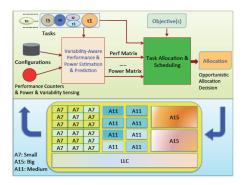

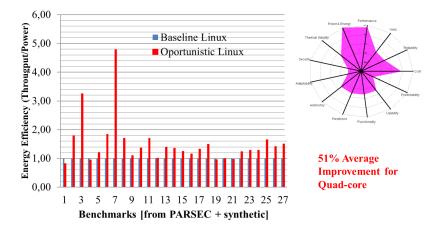

### Improvement of Energy Efficiency

Goal: • Energy Efficiency

Dutt Research Group 2014

### Improvement of Energy Efficiency

Dutt Research Group 2014

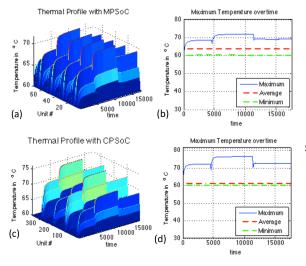

## **Thermal-Aware Performance**

Throughput improvement by 70%-300% for same power and temperature.

On Self-Awareness in CPSoC: Dutt, N.; Jantsch, A. Sarma, S. Self-Aware Cyber-Physical Systems-on-Chip, Proceedings of the International Conference for Computer Aided Design, 2015

Dutt Research Group 2014

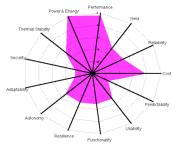

### **Awareness Properties**

- Data abstraction

- Disambiguation

- Desirability mapping

- History maintenance

- Expectations and goals

- On-line learning

- Inspection

Potential benefits by making the devices holistically aware of their situation and purpose.

### **Awareness Properties**

- Data abstraction

- Disambiguation

- Desirability mapping

- History maintenance

- Expectations and goals

- On-line learning

- Inspection

Potential benefits by making the devices holistically aware of their situation and purpose.

$\begin{array}{ll} \leq 1 & mW \\ \leq 1 & mm^2 \end{array}$

# Questions ?