# **Networks on Chip**

10 processors

Axel Jantsch Royal Institute of Technology, Stockholm

December 11, 2002

# **Overview**

- Introduction

- NoC Architecture

- NoC Design Methodology

Introduction 2

# The Challenge

| # Gates | # Processors | Year |

|---------|--------------|------|

|         |              |      |

| 6 M     | 4            | 2000 |

| 24 M    | 16           | 2003 |

| 96 M    | 64           | 2006 |

| 384 M   | 256          | 2009 |

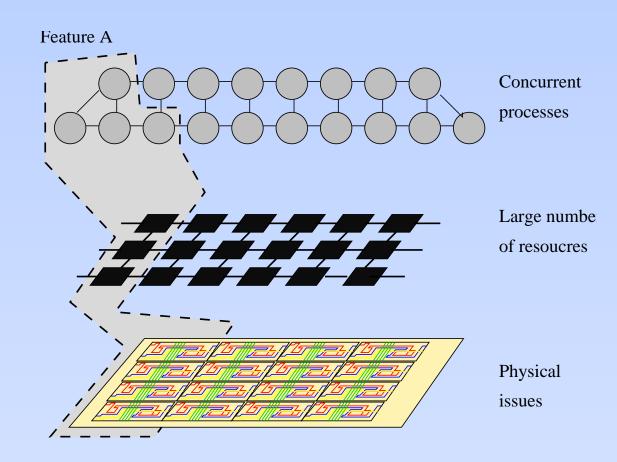

# Functions, Architecture, and Physics

Large number of resoucres

Physical issues

### **Challenge Areas: Physical Issues**

- Deep submicron effects, noise, signal integrity

- Interconnect

- Power consumption, power delivery

- Clock distribution

- Memory integration (50-80% of the chip)

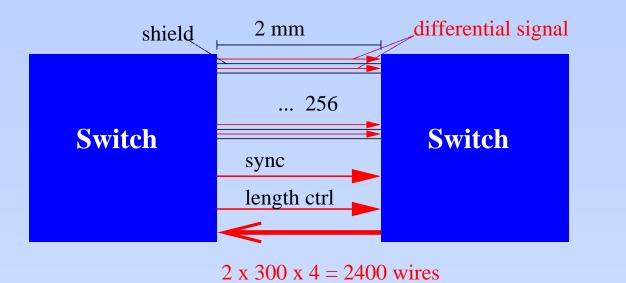

Scenario:

- 60 nm CMOS

- $22 \times 22$  mm Chip size

- $2 \times 2$  mm resource size

- 300 nm minumum wire pitch

- 6600 wires between two resources on each metal layer

# **Challenge Areas: Architecture**

- Communication infra-structure

- ★ Physical layer

- ★ Data link layer

- ★ Network layer

- ★ Transport layer

- Type and size of resources (Micro processor, DSP, memory, FPGA, etc.)

- Resource usage

### **Challenge Areas: Methodology**

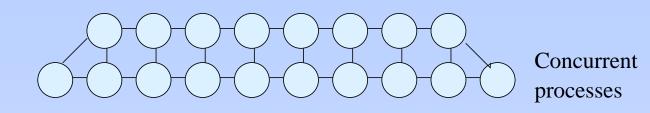

- Specification techniques of concurrent activities

- Performance analysis

- Reuse and Integration of both functions and components

# **Challenge Areas: Run Time Services**

- Monitoring

- Fault-tolerance,

- Diagnostics

- Fault recovery

- Dynamic resource management

### **Challenge Areas: Configurability**

A sensible trade-off between efficiency and generality is critical.

- Configurability of communication resources from the data link to the application layer

- Configurability of resources (processors, DSPs, FPGAs, etc.)

- When and who?

- $\star$  Design-time configuration: Platform  $\Rightarrow$  Pruduct

- $\star$  Static product configuration: Once for a product

- \* Dynamic reconfiguration: Programming of the product

# **NoC Architecture**

- Topology

- Switch Architecture

- Data link layer

- Network layer

- Transport layer

- Application layers

- Regions

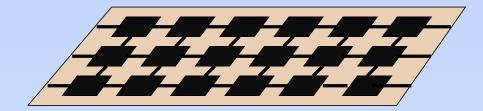

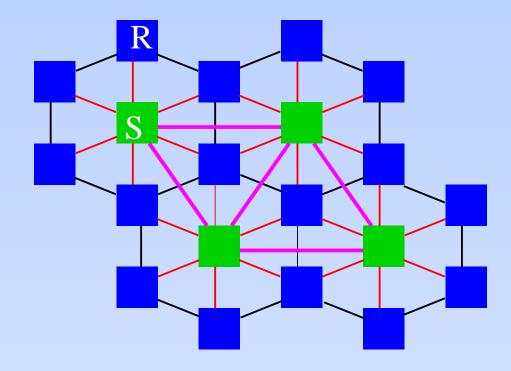

### **Topology: Honeycomb**

- Resource-to-switch ratio: 3

- A switch is connected to 6 resources and 6 switches

- A resource is connected to 3 switches and 3 resources

- Wiring intense topology

- Max number of hops grows with n/3

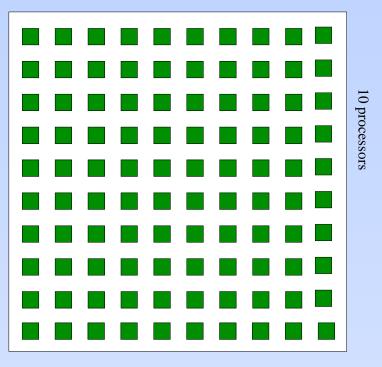

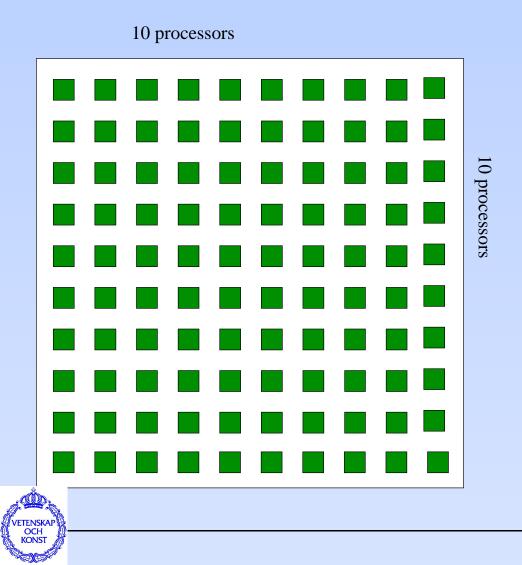

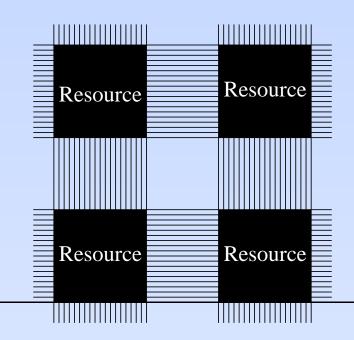

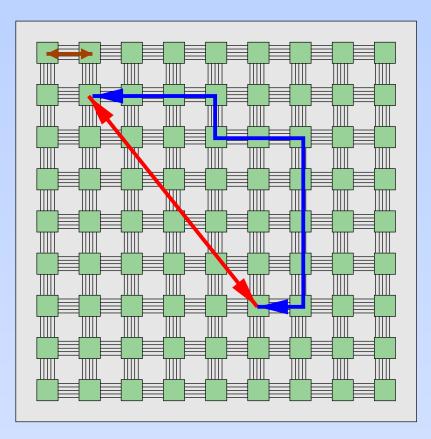

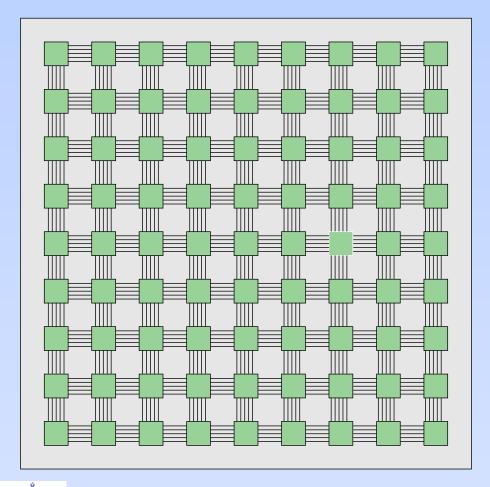

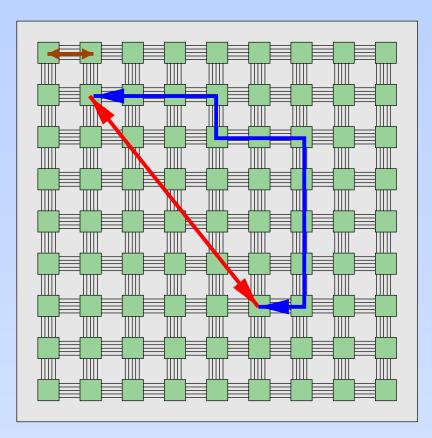

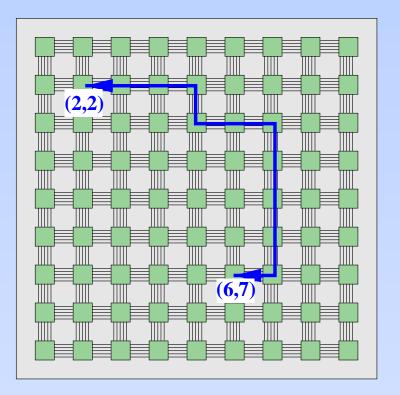

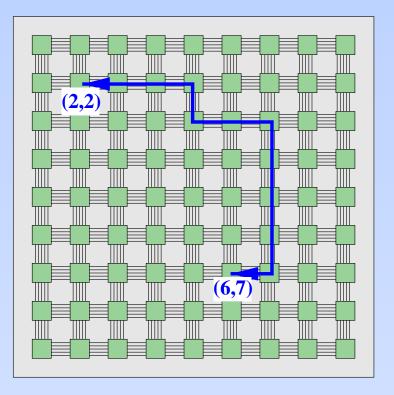

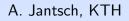

# **Topology: Mesh**

- Resource-to-switch ratio: 1

- A switch is connected to 4 switches and 1 resource

- A resource is connected to 1 switch

- Max number of hops grows with 2n

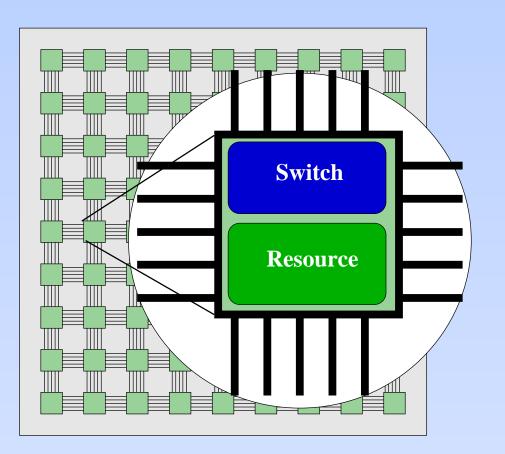

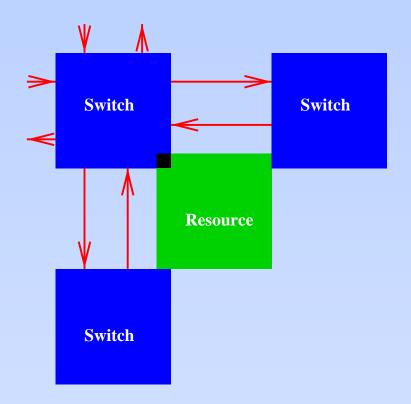

### The Node in a Mesh

- How large are resources and the switches?

- What is the best geometry of switch and resource?

- How many wires and how long?

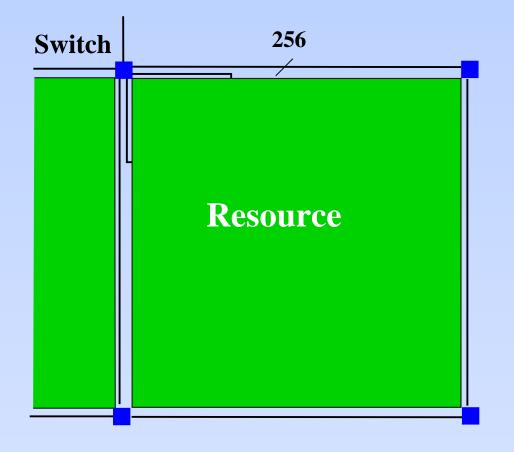

# Square Switch

#### Scenario:

- 60*nm* CMOS

- $22mm \times 22mm$  chip size

- 300nm minimal wire pitch

- $2mm \times 2mm$  resource

- $100 \mu m \times 100 \mu m$  switch

- switch-to-switch connection: 256 wires

- switch-to-resource connection: 256 wires

OCH

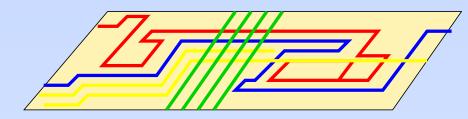

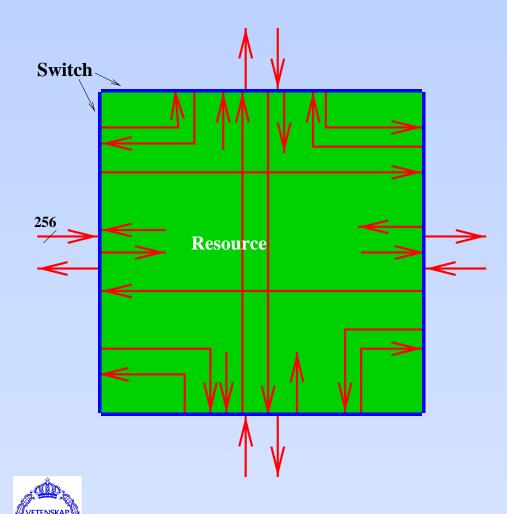

# **Thin Switch**

#### Scenario:

- 60*nm* CMOS

- $22mm \times 22mm$  chip size

- 600nm minimal wire pitch for top layers

- $2mm \times 2mm$  resource

- $4 \times 50 \mu m \times 2000 \mu m$  switch

- switch-to-switch connection: 512 wires

- switch-to-resource connection: 512 wires

# **Communication is Key on Several Levels**

Communication Layers and unit of communication:

- Physical layer: Word

- Data link layer: Cell

- Network layer: Packet

- Transport layer: Message

- Application layer

# **Physical Layer**

- Physical distance

- Number of lines

- Activity control

- Buffers and pipelining

# **Data Link Layer**

- Line frequency versus switch frequency (word versus cell)

- Buffering

- Error correction

- Power optimization; e.g. avoid activity and power optimized encoding

### **Network Layer**

- cell size versus packet size

- Network address scheme,

e.g. 4+4 bit for 16 × 16 resources

- Routing algorithm

- Priority classes: e.g. 2 classes:

- 1. high priority, fixed delay cells

- 2. low priority, best effort delay cells

- Error correction

### **Transport Layer**

- Message size versus cell size

- Virtual channels with traffic profiles

- Signaling

- Priority classes of channels, e.g.

- 1. constant bit rate traffic

- 2. varying bit rate traffic

- Network resource management

- Error correction

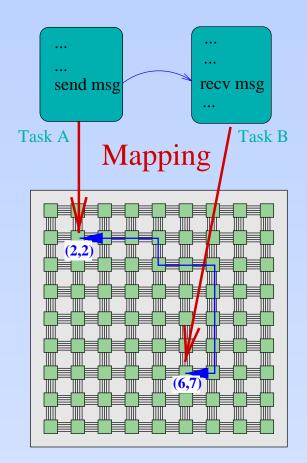

### **Application Layers**

Interprocess communication at the task level:

- send / receive for individual messages

- open; write/read; close for channel based communication

Mapping issues:

- Assigning tasks to resources

- Translating task addresses to resource/task addresses

- Establishing and closing channels

- Static allocation versus dynamic allocation

**Region Wrapper**

**Special**

Purpose Region

# Regions

- Not all resources have the same size; e.g.

- ★ Memory

- ★ FPGA regions

- ★ Special purpose architectures like multiprocessors

- ★ mixed signal parts

- A region wrapper makes the region transparent

- The region wrapper can be

- ★ at several protocol layers,

- $\star$  in hardware or software

- ★ local or distributed

# **NoC Operating System**

- Monitoring

- ★ Utilization of resources and switches

- $\star$  Power consumption

- ★ Statistics (errors, cells, etc.)

- Communication services (transport, presentation and application layers)

- Resource allocation and load migration

- Diagnostics and fault recovery

- Power management

- Development support services

- ★ Libraries for run-time services

- ★ Compilers, linkers and simulators

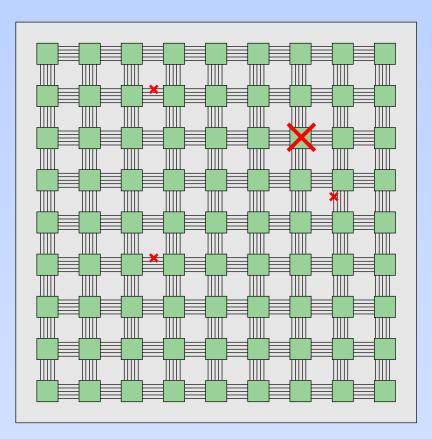

# **Dynamic Fault Handling Example**

#### Assumptions:

- NoC-OS makes run-time diagnostics

- NoC-OS can identify faulty parts

- Network layer protocol can be reconfigured at run-time

- If a resource becomes faulty:

- 1. NoC-OS detects a faulty resource

- 2. NoC-OS defines a new region to isolate the faulty resource

- 3. NoC-OS reconfigures the Network layer protocol to route around the faulty resource

### Summary - NoC Architecture

- The NoC Architecture defines

- $\star$  the communication infrastructure

- ★ the resource-to-network interface

- $\star$  the network services

- Strict layering of communication protocols and services allows

- $\star$  the separation of the network backbone from the resources

- \* combination of different features and functionality at different levels

- $\star$  the customization of a generic platform into an efficient product

# **NoC Design Methodology**

- Design Productivity Gap

- Arbitrary Composability

- Reuse

- Predictability

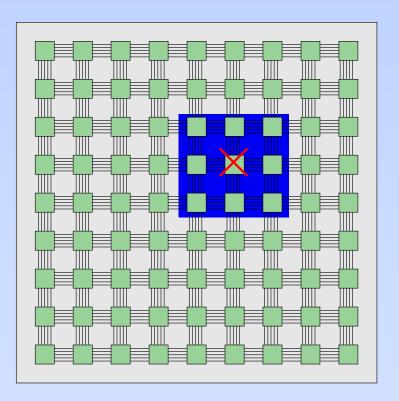

### **Design Productivity Gap**

VETENSKAP OCH KONST

#### International Technology Roadmap for Semiconductors 1999

# **Superexponential Increasing Design Complexity**

| 2                     |                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Functionality + Testability                                                                                                                                          |

| 1 K                   | Functionality + Testability + Wire delay                                                                                                                             |

| s                     | Functionality + Testability + Wire delay + Power management                                                                                                          |

| Number of Transistors | Functionality + Testability + Wire delay + Power management<br>+ Embedded software                                                                                   |

| of Trai               | Functionality + Testability + Wire delay + Power management<br>+ Embedded software + Signal integrity                                                                |

| nber o                | Functionality + Testability + Wire delay + Power management + Embedded<br>software + Signal integrity + RF                                                           |

| Nun                   | Functionality + Testability + Wire delay + Power management + Embedded<br>software + Signal integrity + RF + Hybrid chips                                            |

| 1 Billion             | Functionality + Testability + Wire delay + Power management +Embedded software<br>+ Signal integrity + RF + Hybrid chips + Packaging                                 |

|                       | Functionality + Testability + Wire delay + Power management +Embedded software + Signal<br>Integrity + RF + Hybrid chips + Packaging + Management of physical limits |

#### International Technology Roadmap for Semiconductors 1999

# **Arbitrary Composability**

Given a set of components C and combinators O. Let  $A_1$  be a component assemblage. (C, O) is arbitrary composable if

$A_1 + B \Rightarrow A_2$

can be done for any  $B \in C, + \in O$  without changing the relevant behaviour of  $A_1$ .

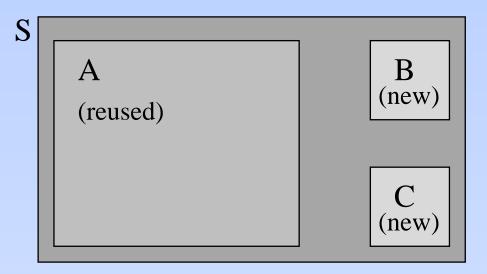

### **Linear Effort Property**

Given a set of components C and combinators O.

Let  $A_1, \ldots, A_n$  be component assemblages. A design process using C and O to build a system has the linear effort property if  $A_1, \ldots, A_n$  can be integrated into a system S with an effort dependent on n but not on the size of the assemblages: leffort(n). Total design effort for S is

$$Deffort(S) = Deffort(A_1) + \cdots + Deffort(A_n) + Ieffort(n)$$

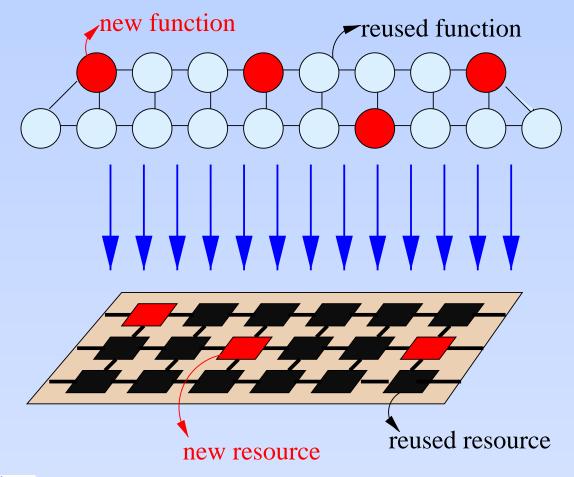

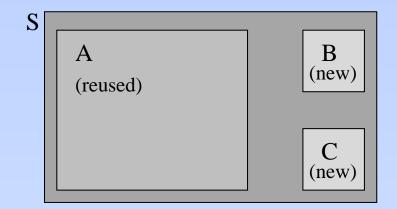

### Reuse

- Components and resources

- Communication infrastructure

- Application parts and feature reuse

- Design, simulation and prototype environment

- Verification effort

# Predictability

- Communication performance

- Electrical properties

- Design and verification time

### **A NoC Based Design Process**

- Configuring the platform

- Selecting resources

- Reuse of features

- Evaluation and integration

# **Design Methodology - Summary**

- A NoC Platform greatly restricts the design space

- It trades in optimality for design efficiency and predictability

- The arbitrary composability and the linear effort properties provide a scalable platform

- Reuse

- Predictability

Further information: www.imit.kth.se/info/FOFU/NOC/