# HW/SW Codesign

May 2001

Axel Jantsch Royal Institute of Technology

### **Overview**

- ☆ Introduction

- ✤ Types of Codesign

✤ Main issues and challanges

☆ Methodology

☆ HW/SW Cosimulation

### Introduction

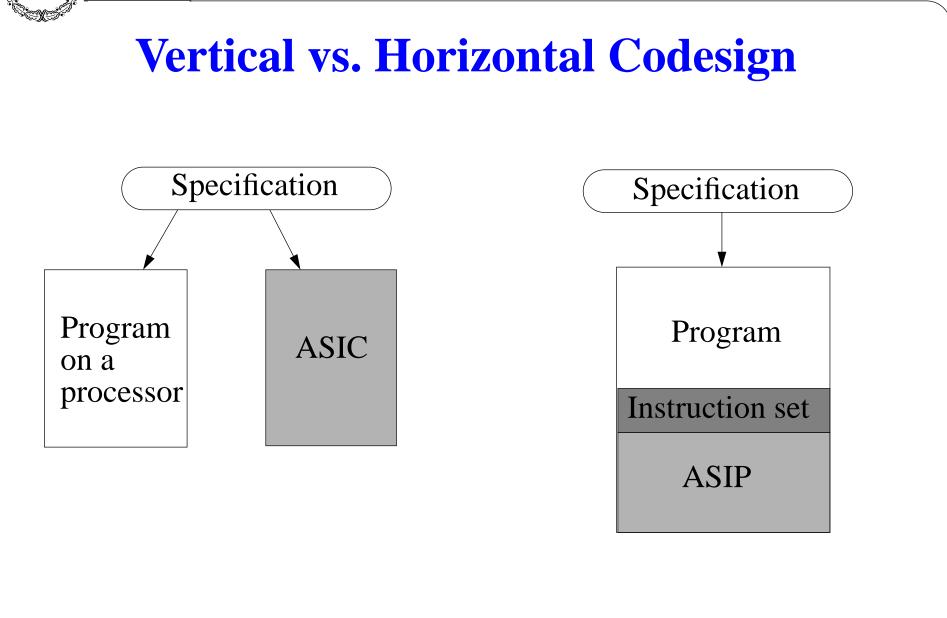

- ☆ Vertical and Horizontal Codesign

- ☆ Figures of merits

- ✤ Favorable for SW

- ☆ Intellectual Property (IP) blocks and Reuse

- ☆ Integration of HW design and SW design

# **Interfaces between HW and SW**

- $\checkmark$  Instruction set

- Standard instruction sets

- + Application specific instruction sets

- ☆ Bus protocol

- ☆ Device drivers

- ☆ FPGA configuration file

- $\checkmark$  Configuration of multiple concurrent resources

- ☆ Compilers

- ☆ Operating system

### **Figures of Merit**

### ☆ Favorable for HW:

- 🕂 Delay

- + Throughput

- + Real-time systems

- + Power

- 🕂 Size

### ☆ Favorable for SW:

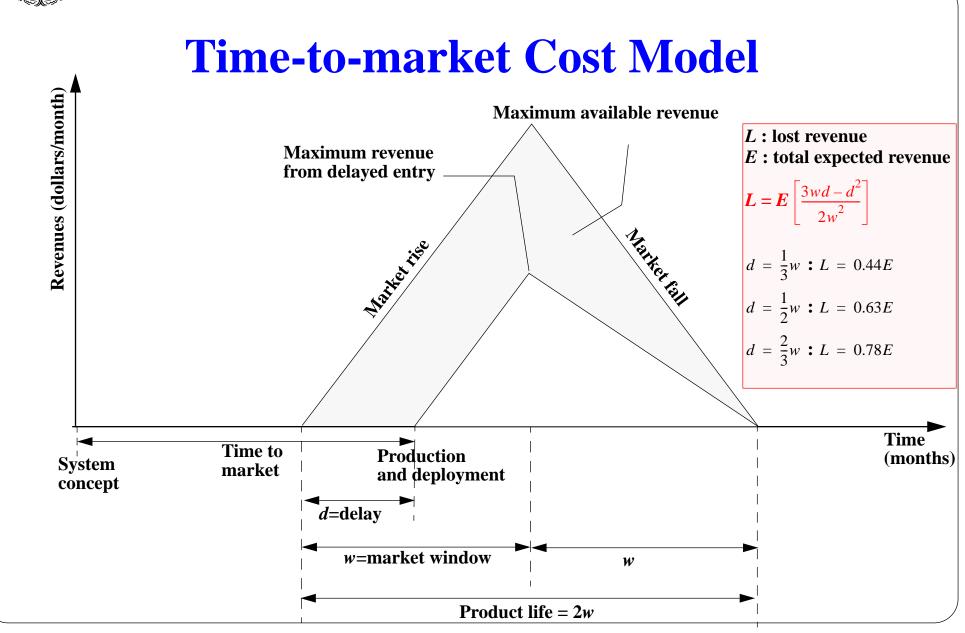

- Time to market

- + Flexibility

- + Volume

### 🛠 Others

- + Cost across products and product families platform

- Design productivity

- + Available tools and methodologies

### **IP and Reuse**

### ☆ Integration of IP blocks

- Development environment and tools

- ✤ Interfaces: HW interfaces, device drivers

+ Testing

+ Business model and legal issues

### ☆ IP Blocks:

Processors

+ DSPs

- Protocol implementations

- Encryption/decryption blocks

- I/O devices

- + Operating systems

ROYAL

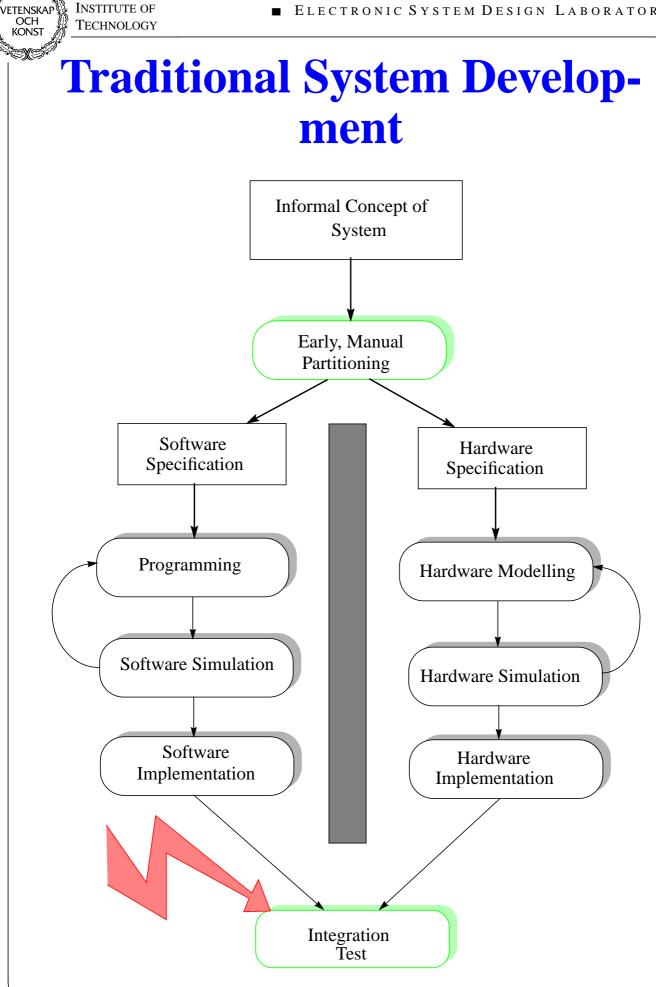

- ☆ Manual partitioning based on a ambiguous and incomplete system specification.

- ☆ Hardware and software development is conducted without sufficient exchange of information.

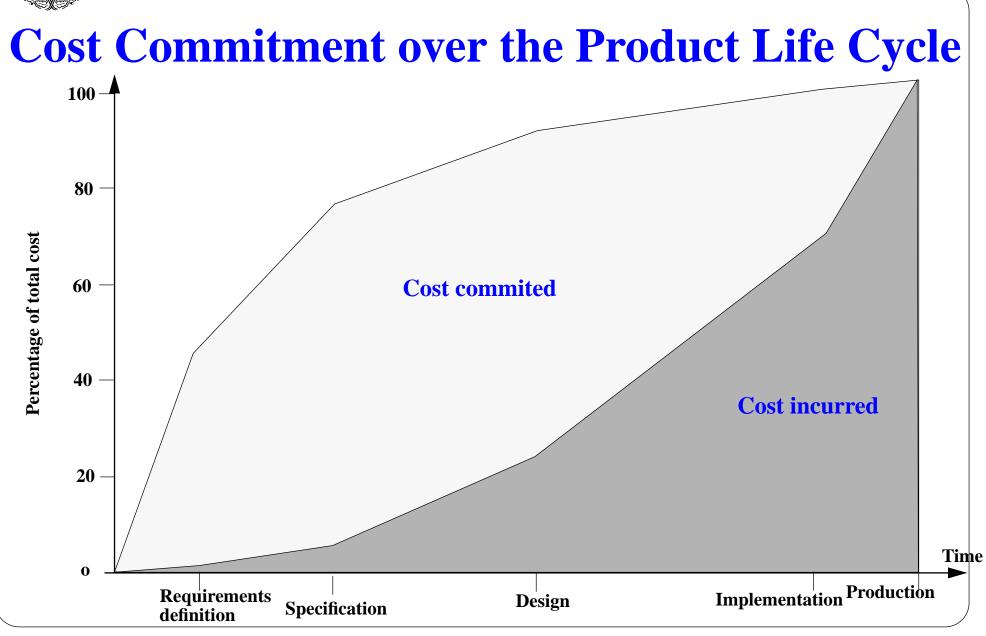

- $\therefore$  Errors that are detected in the integration phase can be very costly.

- ☆ The cost of correcting errors is an exponential function of the time between error generation and error detection.

- ☆ If possible, integration problems are corrected in the software which reduces maintainability and reusability.

- ☆ Because of this danger the hardware is often over-equipped with features that are never used.

ROYAL INSTITUTE OF

TECHNOLOGY

OCH

KONST

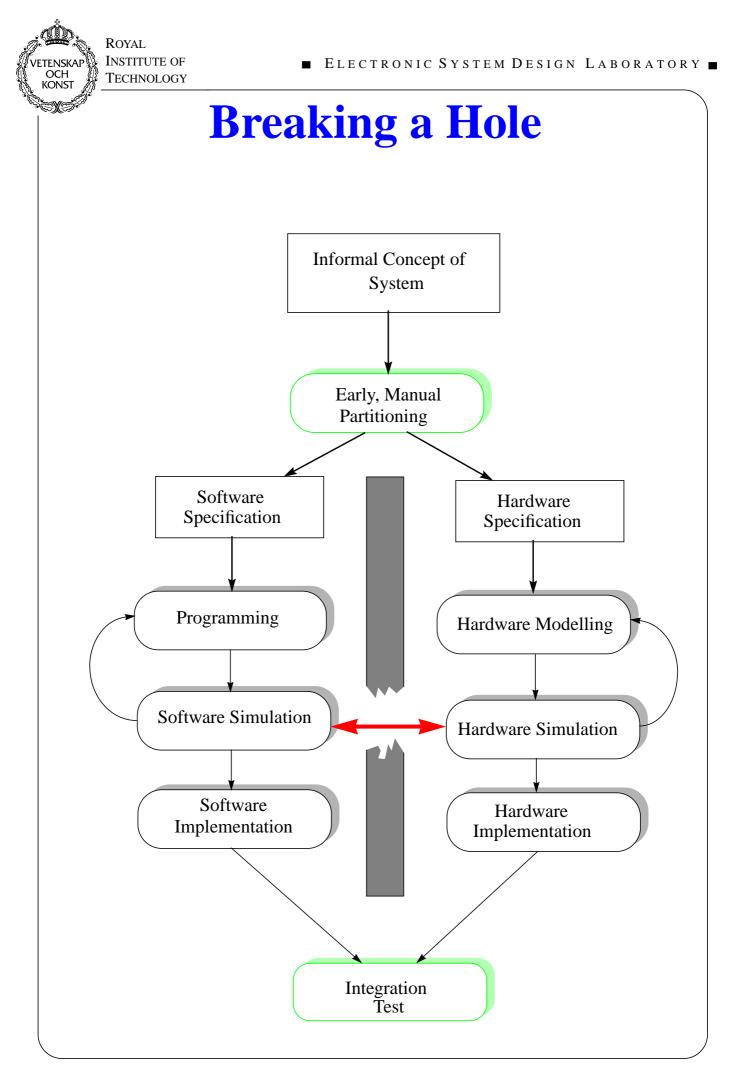

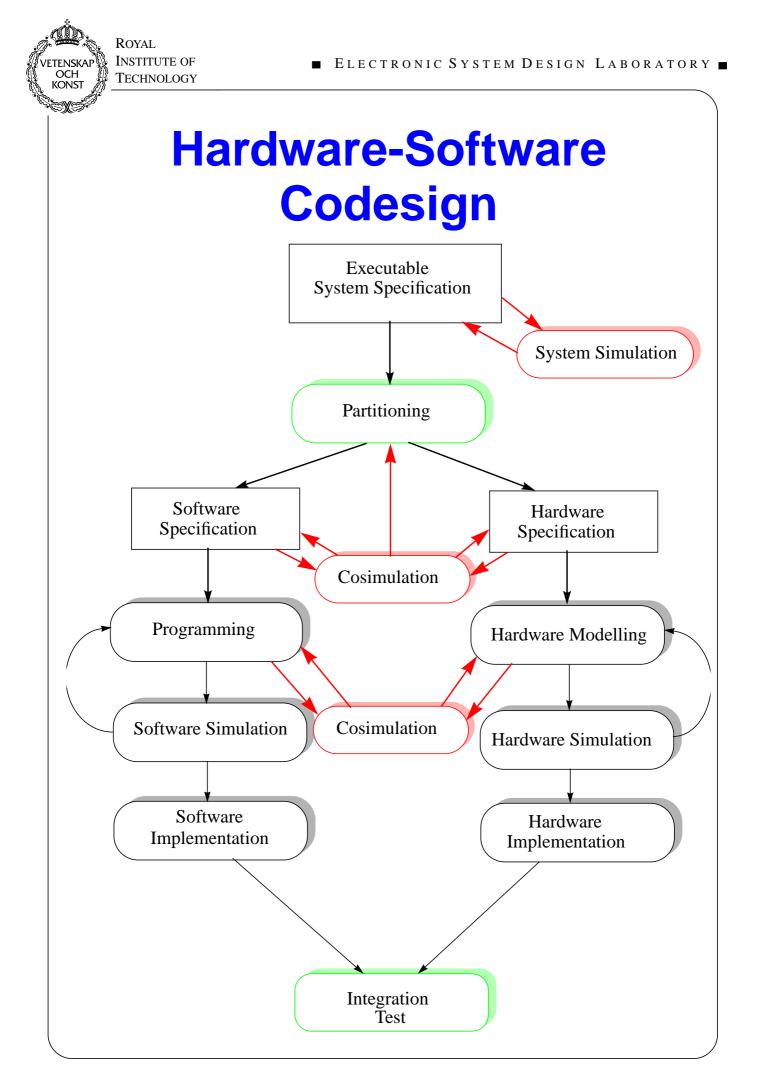

$\Rightarrow$  Specification is more stable.

ROYAL INSTITUTE OF

TECHNOLOGY

TENSK

OCH

KONST

- $\Rightarrow$  Systematic partitioning is less dependent on intuition.

- $\checkmark$  Simulation results from system simulation serve as reference.

- ☆ Avoid multiple test-benches

- $\checkmark$  Errors are detected earlier

- $\checkmark$  Development time is shorter

- $\Rightarrow$  Reusability and maintainability is higher

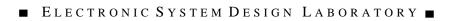

### **Function - Architecture Codesign**

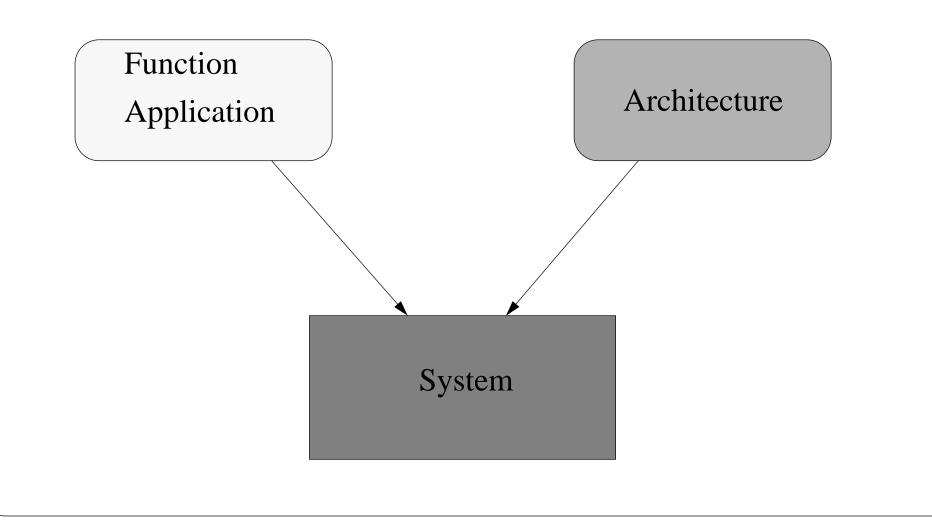

# Methodology

☆ Development phases

$\therefore$  Life cycle models

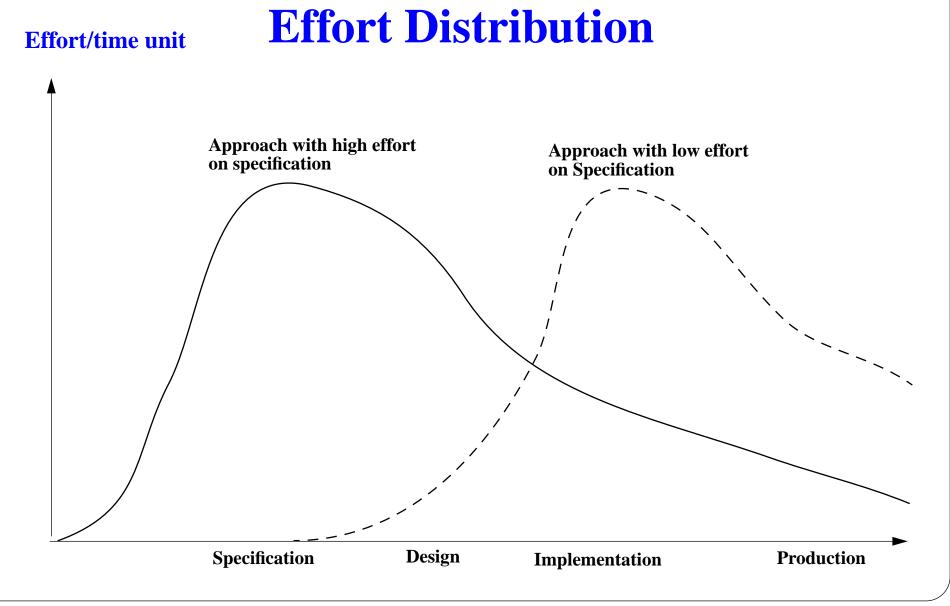

☆ Effort distribution in different phases

# **Involved People**

- ☆ Customers

- 🕂 Users

- Harketing and sales personnel

- Operators

- ✤ Maintenance personnel

- ☆ Product manager

- ☆ Project manager

- ☆ Requirement definition engineer

- ☆ Specification engineer

- 🖈 Designer

- $\Rightarrow$  Implementation engineer

- ☆ Test engineer

### **Life Cycle Models**

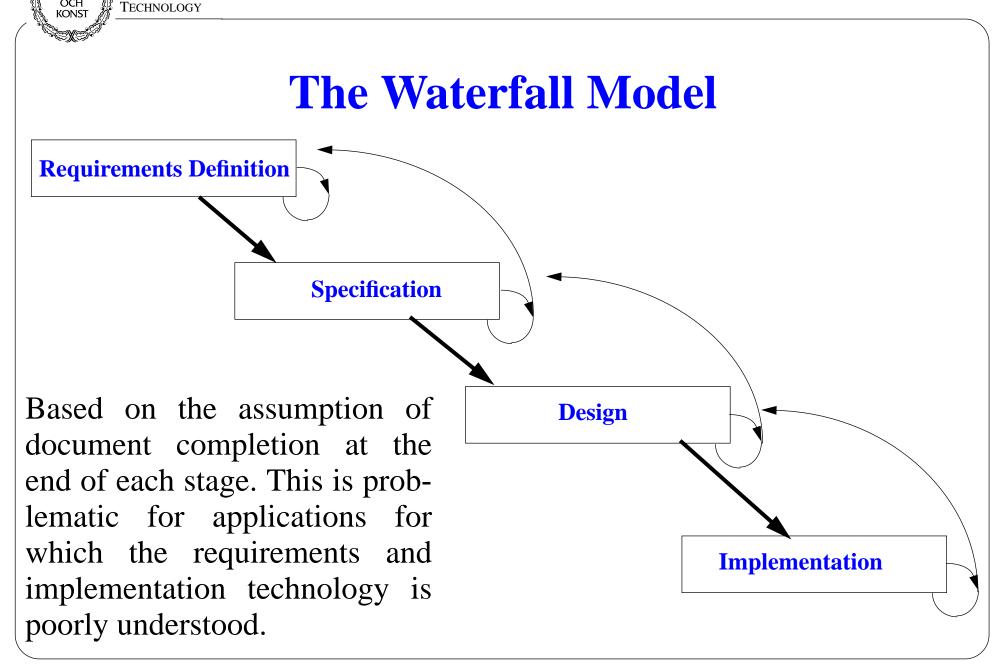

- ☆ Waterfall model

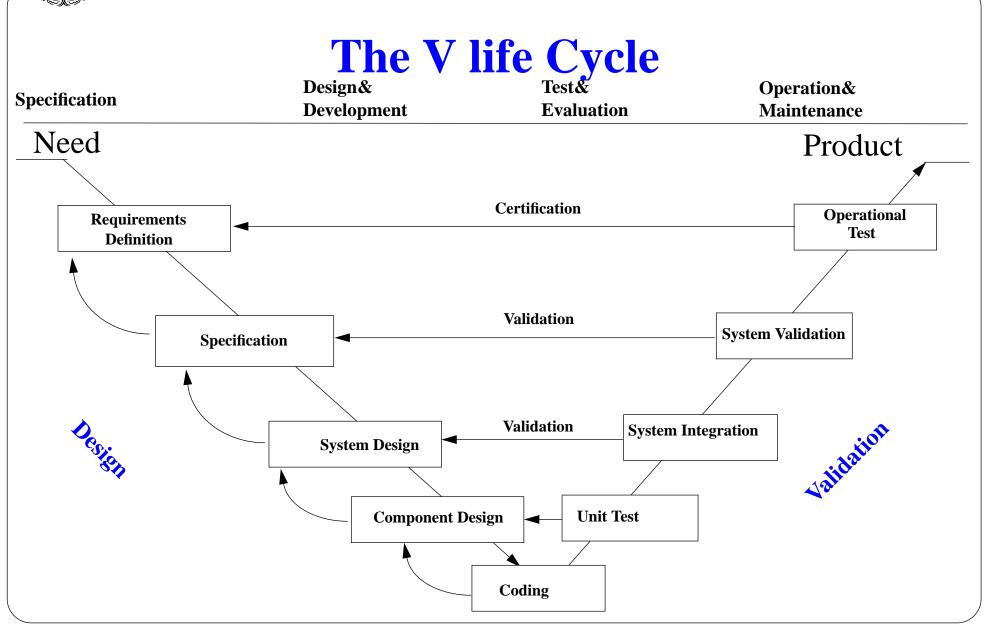

- ☆ V-cycle

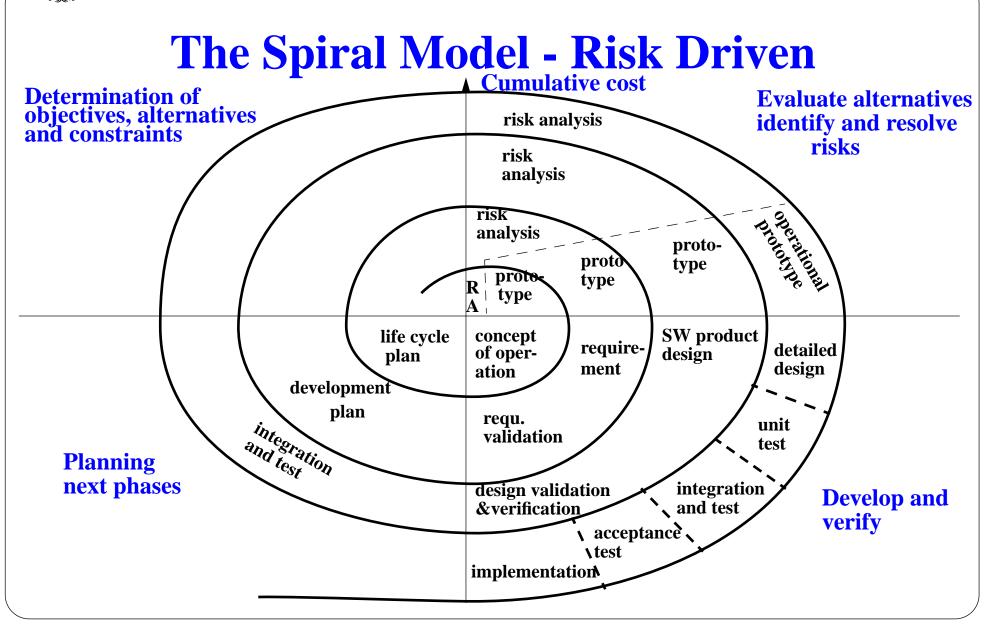

- ☆ Spiral model

ROYAL INSTITUTE OF

OCH

KOYAL VETENSKAP OCH KONST

#### ELECTRONIC SYSTEM DESIGN LABORATORY

ROYAL INSTITUTE OF

TECHNOLOGY

VETENSKAF

OCH

KONST

ROYAL INSTITUTE OF

TECHNOLOGY

etensk. OCH Konst

ROYAL INSTITUTE OF

TECHNOLOGY

etenska OCH Konst

ROYAL INSTITUTE OF TECHNOLOGY

# Codesign Related Tasks -Design

- Specification of functionality as a set of concurrent tasks

- Specification of architecture and resource allocation

- ✤ Type and number of processors

- Operating system

- Communication structure

- ▷ One central bus vs Several separated buses

- Hierarchical bus structure

- Switches

- Protocols

- Data link layer

- Network layer

- Application layer

- Hemory structure and hierarchy

- Shared memory

- Local memory

- Caches Cache coherence

- Memory allocation to different tasks and protection from other tasks

- + Application specific HW resources

- ☆ Task partitioning and binding

- $\checkmark$  Task synthesis and implementation

- ☆ Communication synthesis and implementation

- ☆ System integration

# **Codesign Related Tasks - Performance**

- ☆ System level performance analysis

- + Error rate, failure rate and reliability, buffering requirements, etc.

- ☆ Architecture performance analysis

- Capacity of computation resources

- Capacity of communication resources

- Capacity of storage resources

- Performance of operating systems (context switching, worst case reaction time, etc.)

### ☆ System performance verification

- Performance for each task

- Communication performance

- Hemory size and performance, footprint of SW in the memory

- + Overall cost analysis

- $\Rightarrow$  Worst case and average case performence

- $\checkmark$  Static analysis and simulation and profiling based techniques

# **Codesign Related Tasks - Validation**

- ☆ Validation of requirements ("Do we make the right system?")

- $\checkmark$  Functional validation of the task graph

- ☆ Validation of each task's implementation

- $\checkmark$  Validation of the implementation of the communication between tasks

- System validation ("Did we make the system right?")

### ☆ Simulation

- + Test bench development

- Testcase development

- $\Rightarrow$  Formal verification

- Equivalence checking

- Property checking

- + Theorem proving

# **Models and Languages**

- ☆ System level

- Application oriented (e.g. SDL, Matlab, UML)

- Co-modelling to integrate different application aspects

- $\Rightarrow$  Design and implementation level

- Implementation oriented (e.g. VHDL, C, C++, Esterel, Java)

- Hodelling of the architecture to gain accurate performance estimates by means of simulation and profiling

- Co-modeling to integrate different implementation technologies

# **HW-SW Cosimulation**

### Contents

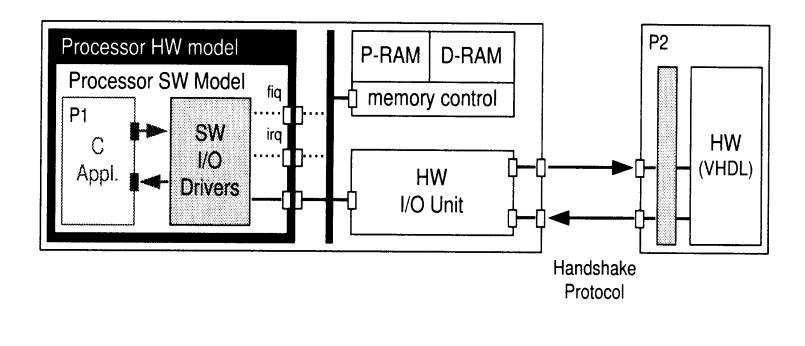

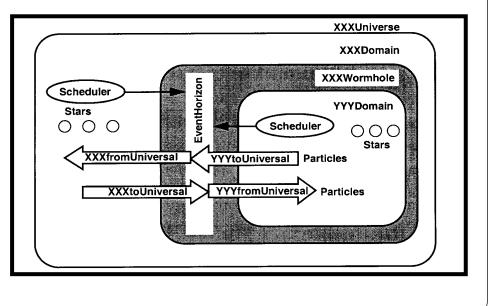

Dimensions of Cosimulation

Communication

Synchronization

Scheduling

Models of Computation

Techniques

Processor Models

Tool Structures

Speed-up Mechanisms

Tool Examples

### Communication

Software Process

ROYAL INSTITUTE OF

TECHNOLOGY

Hardware Process

Underlying interconnection:

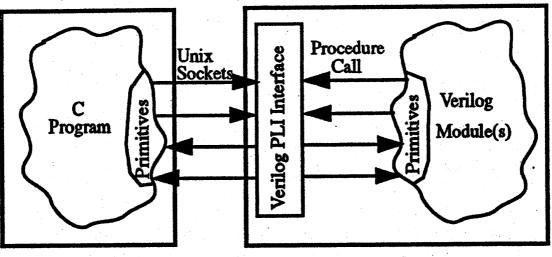

#### ☆ Unix InterProcess Communication (IPC)

- + Pipe

- + Socket Interface

- Remote Procedure Call (RPC)

#### utilized by:

#### ☆ Simulator Interfaces

- + VHDL: Foreign Language Interface

- + Verilog: Programming Language Interface

### ☆ Methods:

- + Shared Memory

- + Message Passing

ROYAL INSTITUTE OF

TECHNOLOGY

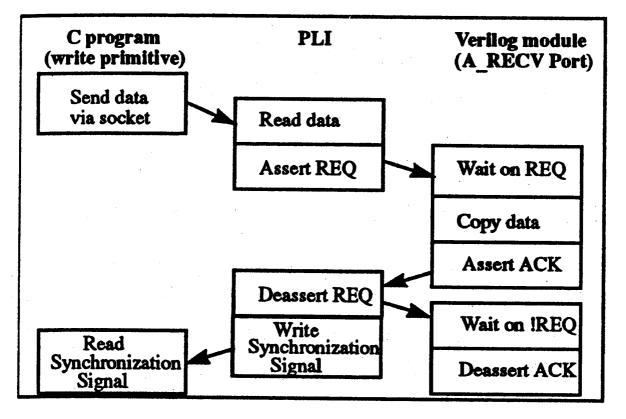

#### ☆ Mechanisms:

- buffered / unbuffered

- 🕂 blocking / non-blocking

- synchronized / unsynchronized data transfer

- + handshaking

# **Scheduling**

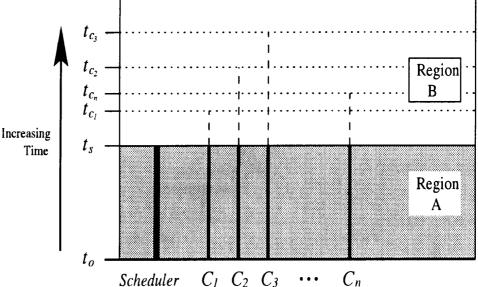

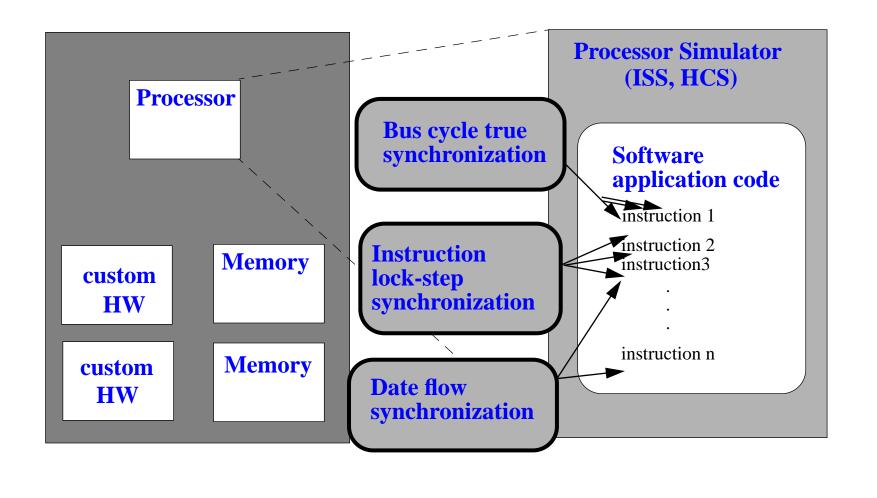

Global Timing Concept: ☆ scheduler keeps global time ☆ each component keeps its local time Scheduling Methods: ☆ conservative scheduling ↑ always: global time ≤ local time ↑ global time monotonously increasing ↑ region A: time has past ↑ region B: *send* actions are allowed; *get* actions block; ☆ optimistic scheduling ↑ *get* actions in region B are allowed.

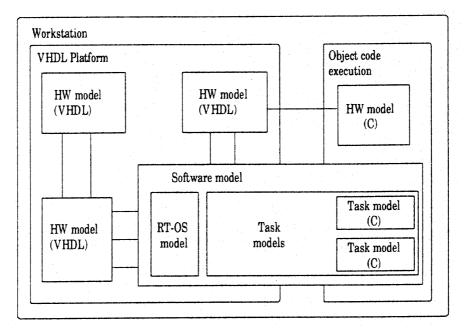

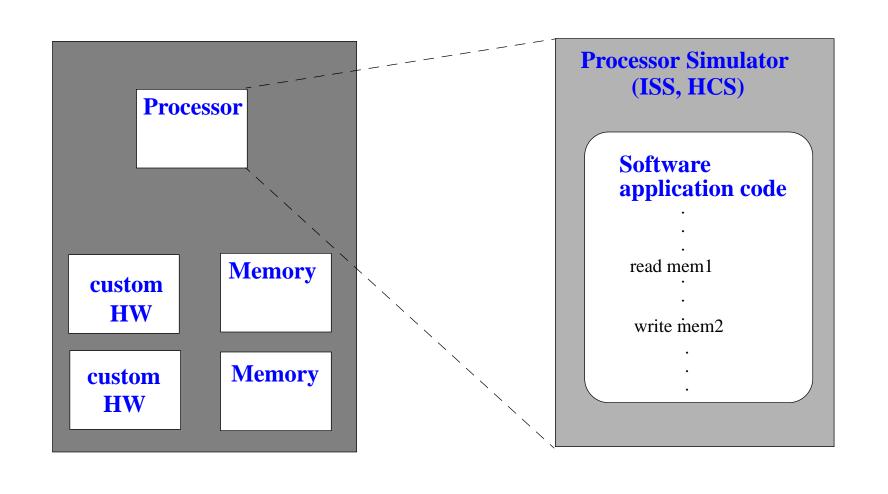

## **Processor Models I**

- ☆ Hardware and software models exist

☆ principles of choice:

- ✤ model availability

- ✤ performance

- timing accuracy

- debugging features

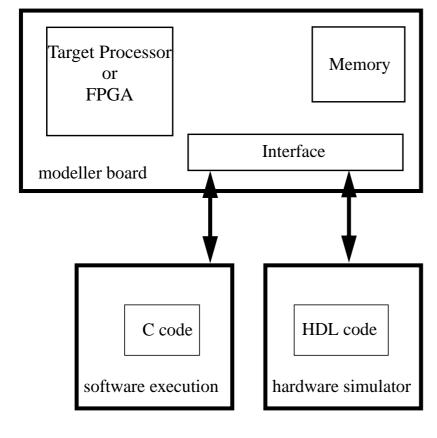

### ☆ Hardware Models

- ✤ logic emulator (FPGA)

#### Hardware Model

#### Software Processor Models

- ✤ nanosecond accurate model

- ✤ cycle accurate model

ROYAL INSTITUTE OF

KONST

TECHNOLOGY

- ✤ instruction set accurate model (ISS)

- ✤ bus functional model (BFM)

#### Techniques Requiring No Processor Model

- ✤ host code execution (HCE)

- + virtual operating system

Virtual Operating System

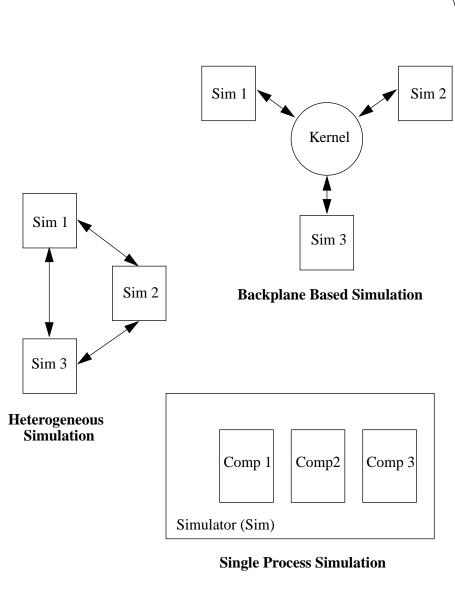

# **Tool Structures**

- ☆ Backplane Based Simulation

- ✤ contains interconnecting kernel

- kernel provides all required translations

- + all signals are translation to a general type

### ☆ Heterogeneous Simulation

- ✤ simulators are directly connected

- explicit control and translation of signals in the simulators

### ☆ Single Process Simulation

- + entire simulation in a single simulator

- + e.g. VHDL-based simulation

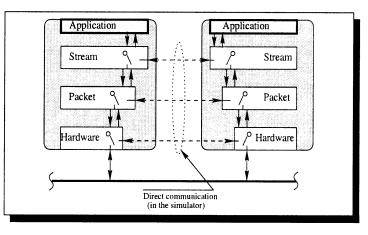

# **Speed-Up Mechanisms**

### ☆ Multiple Communication Models

✤ allow communication on different levels of abstraction

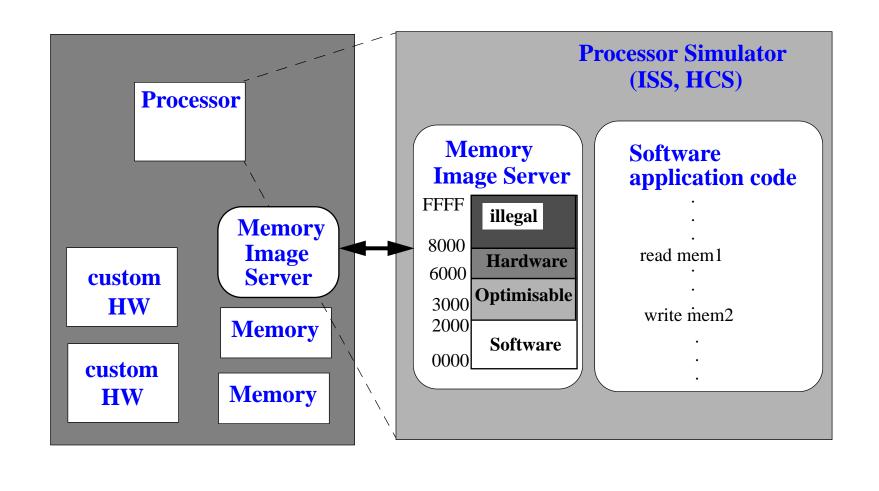

### ☆ Memory Image Server

+ maintain two memory models

### ☆ Distributed Simulation

+ execute the cosimulation on several machines

☆ High Powered Coprocessor

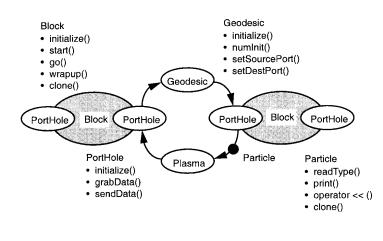

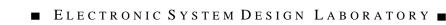

# **Tools I: Ptolemy**

- ☆ developed at University of California at Berkeley

- $\cancel{x}$  simulation framework

- $\checkmark$  written in object-oriented language (C++)

- $\cancel{3}$  build on basic classes

- $\cancel{x}$  allows design of heterogeneous systems

$\checkmark$  designer is enabled to build arbitrary simulation environments

- ☆ Heterogenous simulation environment

- ☆ Different domains for different subsystems

- ☆ General and flexible interface between domains

- ☆ Supported simulation domains:

- Synchronous data flow

ROYAL INSTITUTE OF

TECHNOLOGY

ETENSK/

OCH

KONST

- + Functional simulator for digital hardware

- ✤ Discrete event simulation

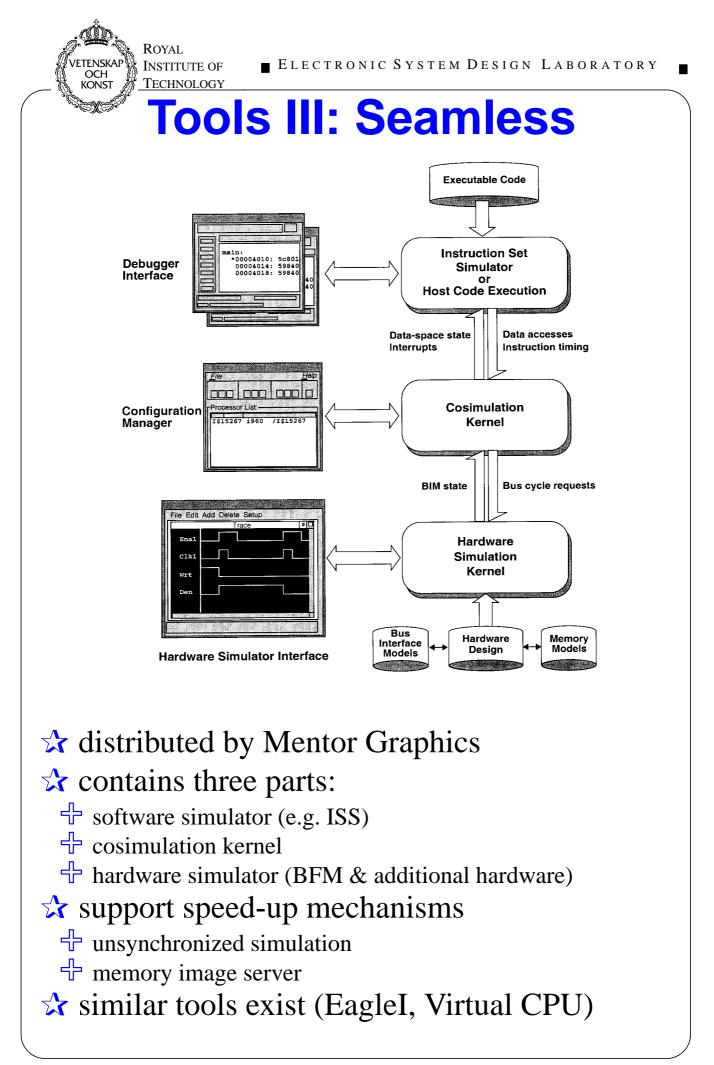

# **Seamless: Memory Model**

# Seamless: Memory Model - cont'd

# **Seamless: Relaxation of Synchronization**

- $\checkmark$  Most electronic systems consist of both HW and SW

- ☆ HW and SW design have different histories, tools, methodologies concepts and require different competence

- ☆ Types of Codeisgn:

- + Vertical Codesign

- + Horizontal Codesign

- 🖈 Tasks

- Hodelling

- 🕂 Design

- ✤ Validation

- ✤ Performance analysis and validation

☆ HW/SW Cosimulation is the most widely used codesign technique