# Adaptive Computing based on FPGA Run-time Reconfigurability

## Ming Liu

Stockholm 2011

Thesis submitted to the Royal Institute of Technology in partial fulfillment of the requirements for the degree of Doctor of Technology Liu, Ming

Adaptive Computing based on FPGA Run-time Reconfigurability

ISBN 978-91-7415-985-1 TRITA-ICT/ECS AVH 11:05 ISSN 1653-6363 ISRN KTH/ICT/ECS/AVH-11/05-SE

Copyright © Ming Liu, April 2011

Royal Institute of Technology School of Information and Communication Technology Department of Electronic Systems Forum 120 SE-164 40 Kista, Sweden

## Abstract

In the past two decades, FPGA has been witnessed from its restricted use as glue logic towards real System-on-Chip (SoC) platforms. Profiting from the great development on semiconductor and IC technologies, the programmability of FPGAs enables themselves wide adoption in all kinds of aspects of embedded designs. Modern FPGAs provide the additional capability of being dynamically and partially reconfigured during the system run-time. The run-time reconfigurability enhances FPGA designs from the sole spatial to both spatial and temporal parallelism, providing more design flexibility for advanced system features.

Adaptive computing delegates an advanced computing paradigm in which computation tasks and resources are intelligently managed in correspondence with conditional requirements. In this thesis, we investigate adaptive designs on FPGA platforms: We present a comprehensive and practical design framework for adaptive computing based on the FPGA run-time reconfigurability. It concerns several design key issues in different hardware/software layers, specifically hardware architecture, run-time reconfiguration technical support, OS and device drivers, hardware process scheduler, context switching as well as Inter-Process Communications (IPC). Targeting a special application of data acquisition (DAQ) and trigger systems in nuclear and particle physics experiments, we set up the data streaming model and conduct theoretical analysis on the adaptive system. Three application studies are employed to verify the proposed adaptive design framework: The first application demonstrates a peripheral controller adaptable system aiming at general embedded designs. Through dynamically loading/unloading a NOR flash memory controller and an SRAM controller, both flash memory and SRAM accesses may be accomplished with less resource consumption than in traditional static designs. In the second case, two real algorithm processing engines are adaptively time-multiplexed in the same reconfigurable slot for particle recognition computation. Experimental results reveal the reduced on-chip resource requirements, as well as an

iv Abstract

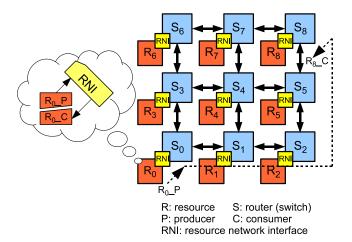

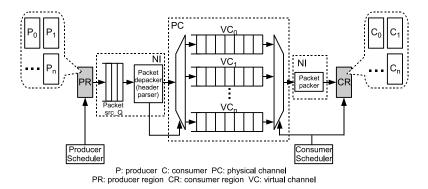

approximate processing capability of the peer static design. Taking advantage of the FPGA dynamic reconfigurability, we present in the third application a novel on-FPGA interconnection microarchitecture named RouterLess NoC (RL-NoC). RL-NoC employs the novel design concept of Move Logic Not Data (MLND), and significantly distinguishes itself from the existing interconnection architectures such as buses, crossbars or NoCs. It does not rely on routers to deliver packets hop by hop as canonical NoCs do, but buffers data packets in virtual channels and brings various nodes using run-time reconfiguration to produce or consume them. In comparison with canonical packet-switching NoCs, the routerless architecture features lower design complexity, less resource consumption, higher work frequency, more efficient power dissipation as well as comparable or even higher packet delivery efficiency. It is regarded as a promising interconnection approach in some design scenarios on FPGAs, especially for light-weight applications.

## Acknowledgments

This thesis project has been carried out under the collaboration between Department of Electronic Systems of Royal Institute of Technology (KTH) in Stockholm, Sweden, and II. Physics Institute of Justus-Liebig-University (JLU) in Giessen, Germany. It was supported in part by BMBF under contract Nos. 06GI9107I and 06GI9108I, FZ-Jülich under contract No. COSY-099 41821475, HIC for FAIR, and WTZ: CHN 06/20.

Most of all, I would like to thank my three supervisors, respectively Professor Wolfgang Kühn, Dr. Zhonghai Lu, and Professor Axel Jantsch for providing me the opportunity to do such an interesting interdisciplinary work. Professor Kühn is my local supervisor in Germany. I learned from him different cultures in physics and also different methods to solve problems. His broad knowledge in physics, computer and electronics areas impresses me very much. I thank him also for his enlightenment in our conversation, especially when I encountered spiritual or technical obstacles in my study and work. Dr. Lu is my direct supervisor who gave me most instructions. He devoted quite much private time on my study. I give my greatest appreciation to him for his fruitful advice on the process of problem targeting, solution proposal, experimental setup and scientific writing. Last but not the least, Professor Jantsch is a very respectable person for his personality, knowledge and inspiration to students. I still clearly remember his words when I was enrolled as a Ph.D student: "Ph.D study is exactly like the sailing Columbus on the sea. You can never know which new land you will arrive at unless you go ahead and try to search for."

I am also thankful to all my colleagues in Giessen and Stockholm. The discussion and suggestion from them are so helpful to improve my professional knowledge and technical skills. My current and previous Giessen colleagues, specifically Jens Sören Lange, Vladimir Pechenov, Geydar Agakishiev, Olga Pechenova, Marco Destefanis, Stefano Spataro, Daniel Kirschner, Johannes Roskoss, Camilla Kirchhübel, Andreas Kopp, Johannes Lang, Zoltán Gagyi-

Pálfy, Thomas Gessler, David Münchow, Ingo Heller, Matthias Ullrich, Marcel Werner, Martin Galuska, Stephanie Künze, Sören Fleischer, Björn Spruck, Yutie Liang, Li Lu, and so on, explained me plenty of physics background knowledge which makes me understand the application very clearly. I also thank Ingo Sander, Johnny Öberg, and Vladimir Vlassov for their interesting lectures and discussion on the modern techniques, as well as Huimin She, Jun Zhu, Liang Rong, Geng Yang, Xiaolong Yuan, Zhuo Zou, Peng Wang and Jiayi Zhang for exchanging our experience of Ph.D study. Many thanks are given to our Chinese collaboration group in Beijing, including Zhen'an Liu, Hao Xu, Qiang Wang, Dapeng Jin for their nice work on the compute node PCB design.

I appreciate Christa Momberger, Thomas Köster, Lena Beronius, Agneta Herling and Alina Munteanu for their administrative and non-technical assistance in travel arrangements, device ordering, and many other issues.

Many thanks to all our international collaboration group members in Munich, Darmstadt, Jülich, Cracow, Uppsala, and other cities. Due to the large quantity I cannot list all the names here. I appreciate very much for our delightful technical discussion in collaboration meetings.

Greatest thanks to my parents and relatives who are far away in China. Their continuous encouragement and support gave me strength to overcome any kind of difficulties in all aspects. I want to tell them loudly, Mama and Papa, thank you for your endless support on my study. I love you!

Special thanks go to my girlfriend Shuo who accompanies me through the life in Europe. I will forever remember the days we spent together, busily but happily.

Ming Liu

April 2011, Giessen

## **Contents**

| Abbreviations |      |                                            | xvii |

|---------------|------|--------------------------------------------|------|

| 1             | Intr | roduction                                  | 3    |

|               | 1.1  | FPGA and Reconfigurable Computing          | 3    |

|               | 1.2  | FPGA-based System Examples                 |      |

|               | 1.3  | Motivation                                 |      |

|               | 1.4  | Thesis Outline and Author's Contributions  |      |

| <b>2</b>      | App  | plication Background                       | 17   |

|               | 2.1  | Nuclear and Particle Physics Experiments   | 17   |

|               | 2.2  | DAQ and Trigger System                     |      |

|               | 2.3  | Design Challenges                          | 22   |

| 3             | Des  | sign Framework for Adaptive Computing      | 27   |

|               | 3.1  | Related Work                               | 28   |

|               | 3.2  | Overview of FPGA PR Technology             | 30   |

|               | 3.3  | Hardware Architecture                      |      |

|               | 3.4  | Run-time Reconfiguration Technical Support | 33   |

|               |      | 3.4.1 ICAP Designs                         |      |

|               |      | 3.4.2 Experimental Results                 | 36   |

|               |      | 3.4.3 Virtual Configurations               | 38   |

|               | 3.5  | OS and Device Drivers                      |      |

|               | 3.6  | Reconfiguration Scheduler                  |      |

|               | 3.7  | Context Switching                          |      |

|               | 3.8  | Inter-Process Communications               |      |

|               |      | 3.8.1 IPC Approaches                       |      |

|               |      | 3.8.2 Pipe-based IPC Models                |      |

|               |      | 3.8.3 Performance Analysis                 |      |

viii Contents

|   |                                                         | 3.8.4 Hardware Implementation of Pipes                   | 55<br>58     |  |

|---|---------------------------------------------------------|----------------------------------------------------------|--------------|--|

|   |                                                         | 3.8.6 Result Matching with Formulas                      | 61           |  |

|   | 3.9                                                     | Summary                                                  | 62           |  |

|   | 0.0                                                     | Summery                                                  | 02           |  |

| 4 | Cas                                                     | se Study 1: A Peripheral Controller Adaptable System     | 67           |  |

|   | 4.1                                                     | Background and Motivation                                | 67           |  |

|   | 4.2                                                     | System Implementation                                    | 69           |  |

|   | 4.3                                                     | Results                                                  | 72           |  |

|   | 4.4                                                     | Summary                                                  | 73           |  |

| 5 | $\mathbf{Ada}$                                          | aptive Computing in Correlated Multi-stream Processing   | 77           |  |

|   | 5.1                                                     | Related Work                                             | 78           |  |

|   | 5.2                                                     | Correlated Multi-streaming Models                        | 78           |  |

|   |                                                         | 5.2.1 Static Model                                       | 78           |  |

|   |                                                         | 5.2.2 Adaptive Model                                     | 81           |  |

|   | 5.3                                                     | Experiments                                              | 82           |  |

|   |                                                         | 5.3.1 Experimental Setup                                 | 82           |  |

|   |                                                         | 5.3.2 Results                                            | 85           |  |

|   | 5.4                                                     | Summary                                                  | 88           |  |

| 6 | Case Study 2: Adaptive Particle Recognition Computation |                                                          |              |  |

|   | 6.1                                                     | Application Introduction                                 | <b>91</b> 91 |  |

|   | 6.2                                                     | System Implementation                                    | 93           |  |

|   | 6.3                                                     | Experimental Results                                     | 96           |  |

|   | 6.4                                                     | Summary                                                  | 98           |  |

| 7 | Cas                                                     | se Study 3: A Light-weight Routerless NoC Infrastructure | 1በ3          |  |

| • | 7.1                                                     |                                                          | 103          |  |

|   | 7.2                                                     |                                                          | 105          |  |

|   | 7.3                                                     |                                                          | 106          |  |

|   | 7.4                                                     |                                                          | 107          |  |

|   |                                                         |                                                          | 107          |  |

|   |                                                         |                                                          | 109          |  |

|   |                                                         | e v                                                      | 110          |  |

|   |                                                         |                                                          | 111          |  |

|   | 7.5                                                     | <u> </u>                                                 | 115          |  |

|   | 7.6                                                     | 1                                                        | 116          |  |

|   |                                                         |                                                          | 116          |  |

|   |                                                         |                                                          | 117          |  |

Contents ix

|              | 7.7<br>7.8 | Power Analysis                                  |     |

|--------------|------------|-------------------------------------------------|-----|

| 8            | Con        | iclusion and Open Issues                        | 127 |

|              | 8.1        | Conclusion                                      | 127 |

|              | 8.2        |                                                 |     |

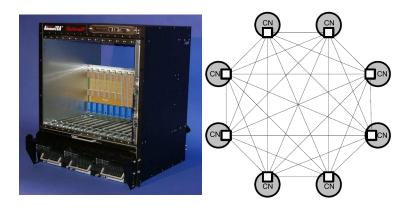

| $\mathbf{A}$ | Des        | ign and Development of ATCA-based Compute Node  | 133 |

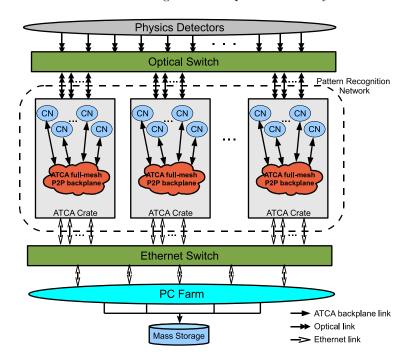

|              | A.1        | Global Computation Network                      | 133 |

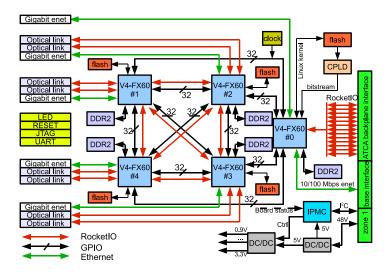

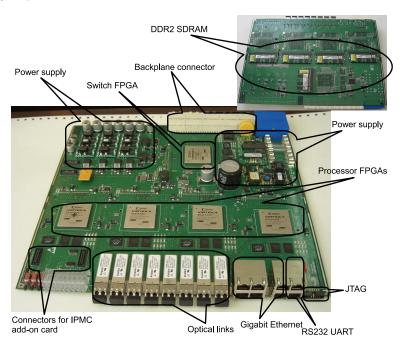

|              |            | Compute Node                                    |     |

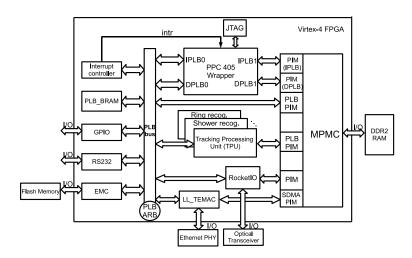

|              |            | HW/SW Co-design of the System-on-an-FPGA        |     |

|              |            | A.3.1 Partitioning Strategy                     |     |

|              |            | A.3.2 Hardware Design                           |     |

|              |            | A.3.3 Software Design                           |     |

| В            | Imp        | elementation of Particle Recognition Algorithms | 141 |

|              | B.1        |                                                 | 141 |

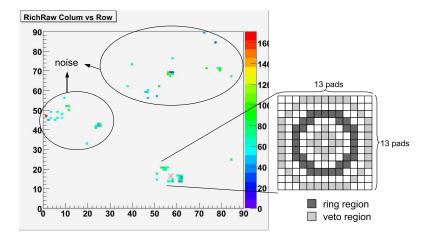

|              | B.2        | Ring Recognition on RICH                        |     |

|              | В.3        | Implementation                                  |     |

|              | B.4        | Results                                         |     |

|              |            | B.4.1 Implementation Results                    |     |

|              |            | B.4.2 Performance Estimation                    | _   |

| Re           | efere      | nces                                            | 153 |

# List of Figures

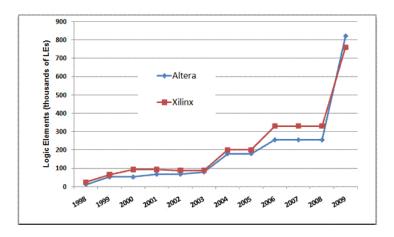

| 1.1  | The largest FPGA announced by Xilinx and Altera (by equivalent 4-input LEs) [2] | 4  |

|------|---------------------------------------------------------------------------------|----|

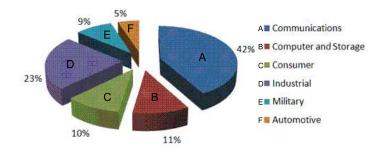

| 1.2  | PLD market by end applications in the third quarter of 2009 .                   | 5  |

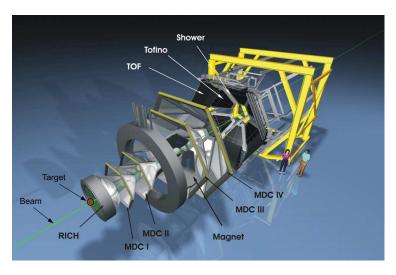

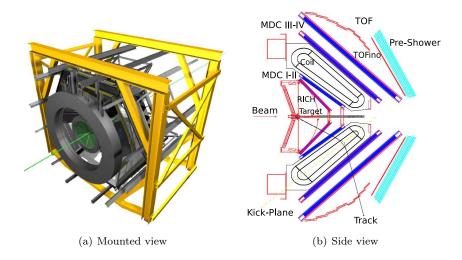

| 2.1  | Dismounted view of the HADES detector system                                    | 18 |

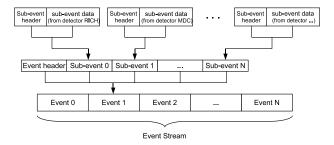

| 2.2  | Event structure consisting of sub-events from different detectors               | 19 |

| 2.3  | Experiments with different event sizes and reaction rates                       | 19 |

| 2.4  | Multi-streaming data flow in DAQ and trigger systems                            | 20 |

| 3.1  | Hardware/software layers of the adaptive system                                 | 28 |

| 3.2  | Partially reconfigurable design on Xilinx FPGAs                                 | 30 |

| 3.3  | Xilinx PR design flow                                                           | 31 |

| 3.4  | The hardware infrastructure of the PR system                                    | 32 |

| 3.5  | The ICAP primitive on Xilinx FPGAs                                              | 34 |

| 3.6  | Structure of the Xilinx ICAP designs                                            | 35 |

| 3.7  | Structure of MST_ICAP and BRAM_ICAP                                             | 35 |

| 3.8  | Reconfiguration performance of ICAP designs                                     | 37 |

| 3.9  | Virtual reconfigurations on multi-context FPGAs                                 | 39 |

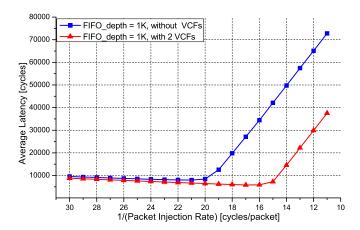

| 3.10 | Timing diagrams of PR designs without or with VCFs                              | 40 |

| 3.11 | Virtual reconfigurations on single-context FPGAs                                | 40 |

| 3.12 | Experimental setup of the consumer-reconfigurable design                        | 41 |

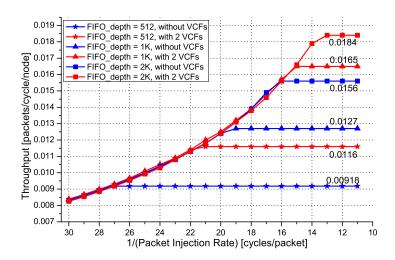

| 3.13 | Throughput measurement results (reconfiguration time = $10 \mu s$ )             | 42 |

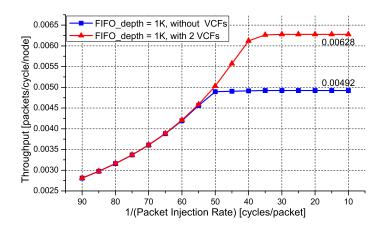

| 3.14 | Throughput measurement results (reconfiguration time = $50 \mu s$ )             | 43 |

| 3.15 | Latency measurement results (reconfiguration time = $10 \mu s$ ).               | 44 |

| 3.16 | Contextless module switching in the reconfigurable design                       | 48 |

|      | Context saving and restoring in the reconfigurable design                       | 49 |

|      | IPC approaches among reconfigurable modules located in vari-                    |    |

|      | ous PRRs                                                                        | 50 |

xii List of Figures

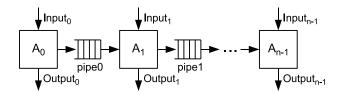

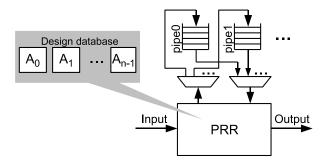

| 3.19 | Consecutive pipe communications between algorithms or algorithm steps |

|------|-----------------------------------------------------------------------|

| 3 20 | Pipe communications in PR designs                                     |

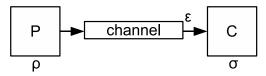

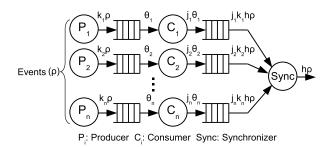

|      | TE definition in the producer-consumer model                          |

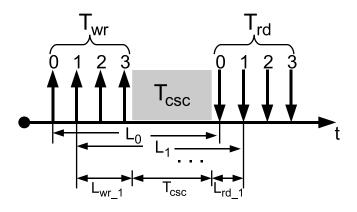

|      | Packet latency in the reconfigurable model                            |

|      | · · · · · · · · · · · · · · · · · · ·                                 |

|      | 1 1                                                                   |

|      | 1 1                                                                   |

|      | 1 1                                                                   |

|      | 1                                                                     |

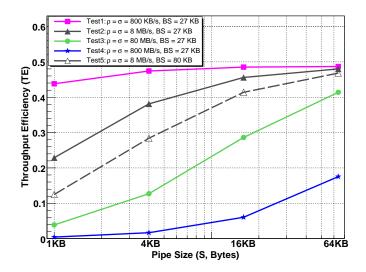

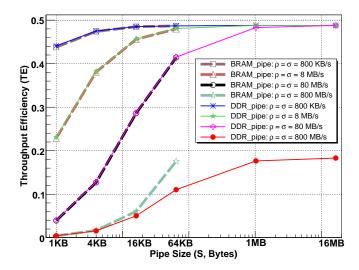

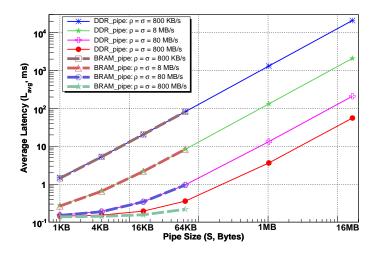

|      | TE comparison of BRAM_pipe and DDR_pipe                               |

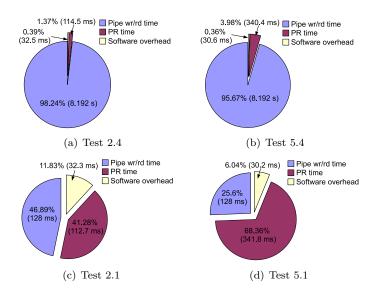

| 3.28 | Latency measurements on BRAM_pipe and DDR_pipe 62                     |

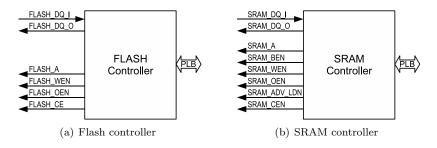

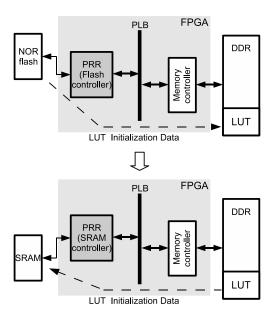

| 4.1  | Blackboxes of the flash controller and the SRAM controller 68         |

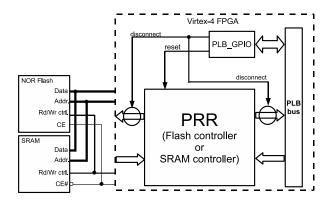

| 4.2  | Hardware structure of the flash/SRAM PR design 69                     |

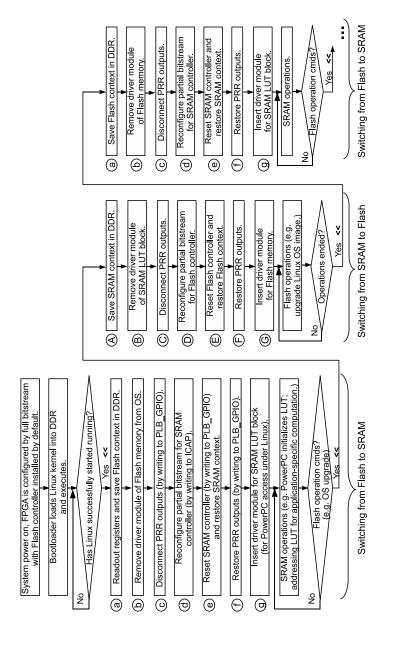

| 4.3  | Flow chart of multiplexing flash/SRAM in Linux 71                     |

| 4.4  | Migrating LUT initialization data from the flash memory to the        |

|      | SRAM                                                                  |

| 4.5  | Implementation of the flash and the SRAM controller within            |

|      | the PRR on a Virtex-4 FX20 FPGA                                       |

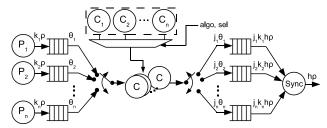

| 5.1  | Static SDF model for multi-streaming applications 79                  |

| 5.2  | Adaptive SDF model for multi-streaming applications                   |

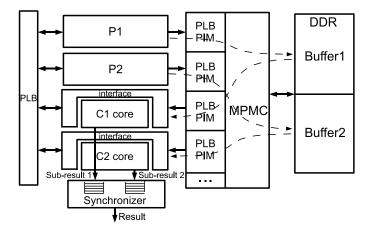

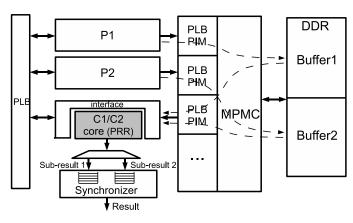

| 5.2  | Implementation of multi-streaming models on the FPGA 83               |

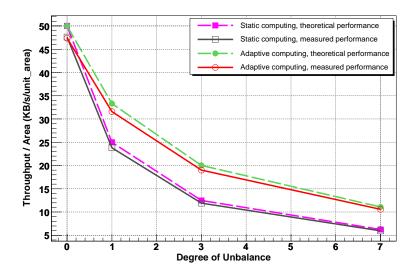

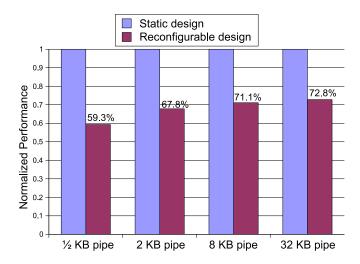

| 5.4  | Result throughput-per-unit-area of static/adaptive computing . 87     |

| 0.4  | rtesuit throughput-per-unit-area of static/adaptive computing.        |

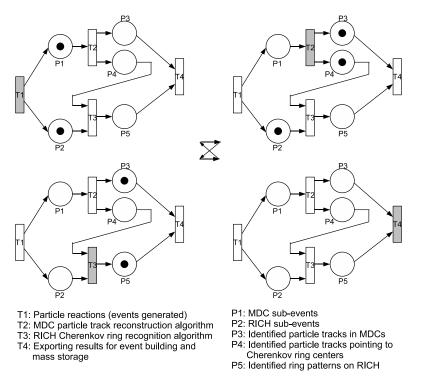

| 6.1  | Petri Net model of the application computation 92                     |

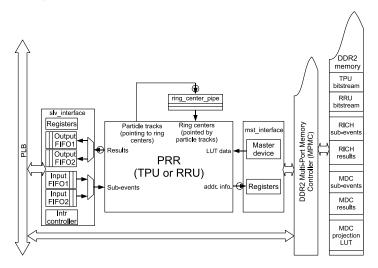

| 6.2  | Static implementation of algorithm engines for particle recogni-      |

|      | tion computation                                                      |

| 6.3  | Reconfigurable implementation of algorithm engines for particle       |

|      | recognition computation                                               |

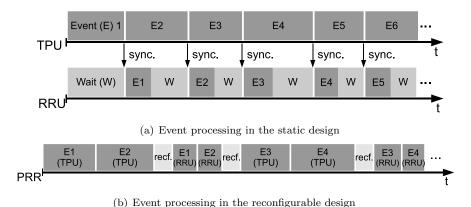

| 6.4  | Event processing time diagram of TPU and RRU 97                       |

| 6.5  | Normalized performance of the reconfigurable TPU/RRU design $$ 98     |

| 7.1  | A typical 2D-mesh network architecture                                |

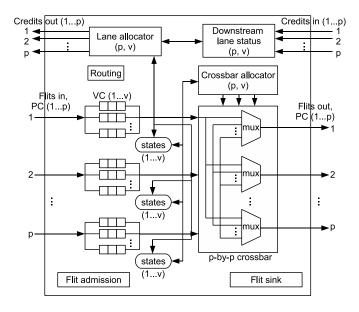

| 7.2  | A canonical wormhole router structure                                 |

| 7.3  | The light-weight routerless NoC                                       |

| 7.4  | Node design with coupled producer-consumer in RL-NoC 110              |

| 7.5  | Duplicated PCs for increasing communication bandwidth 112             |

| 7.6  | An application example of grouping communications in RL-NoC 113       |

|      | The application chample of grouping communications in the 100 110     |

List of Figures xiii

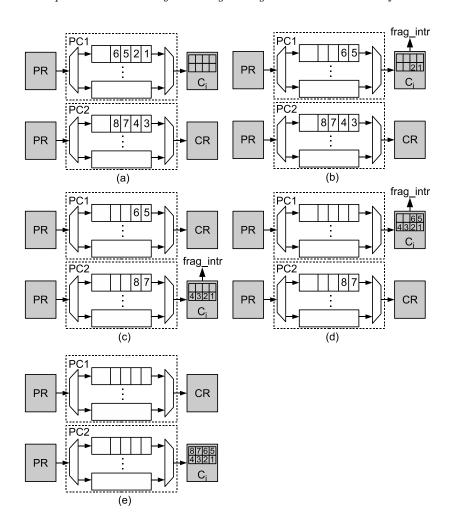

| 7.7        | In-order packet delivery in duplicated PCs. In case of packet            |     |

|------------|--------------------------------------------------------------------------|-----|

|            | flow fragmentation, the active consumer node stops reading the           |     |

|            | current VC and raises an interrupt to the scheduler. It volun-           |     |

|            | tarily gives up the utilization of the consumer region and waits         |     |

|            | to retrieve in-order packets from other PCs                              | 114 |

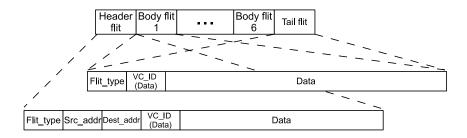

| 7.8        | Packet structure of WH-NoC and RL-NoC                                    | 117 |

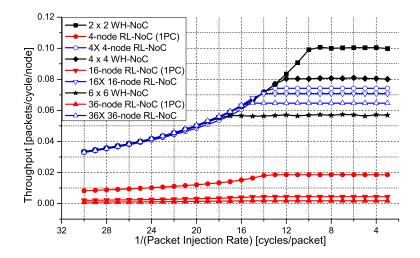

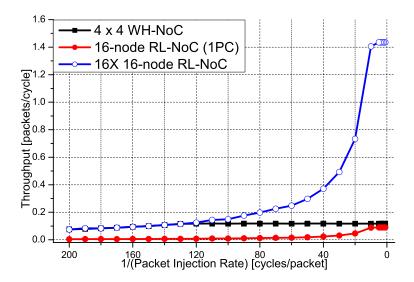

| 7.9        | Throughput comparison of various network sizes                           | 118 |

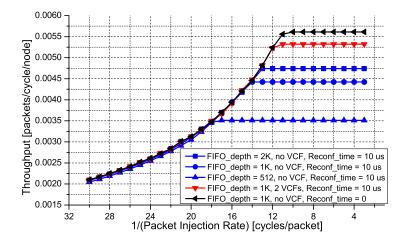

| 7.10       | Throughput of various flit FIFO depths in RL-NoC                         | 119 |

| 7.11       | Throughput comparison in the hotspot traffic pattern                     | 120 |

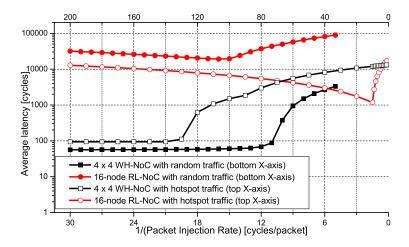

| 7.12       | Latency comparison in the random/hotspot traffic pattern                 | 121 |

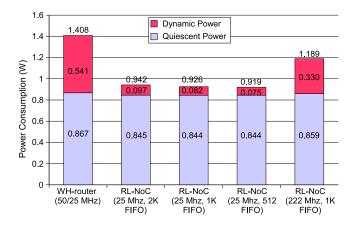

| 7.13       | Power consumption of WH-router and RL-NoC                                | 123 |

| A.1        | ATCA crate and full-mesh backplane (only 8 nodes shown)                  | 134 |

| A.1<br>A.2 | - \ * * /                                                                | 134 |

| A.Z        | erarchical architecture constituted by interconnected compute            |     |

|            | nodes.                                                                   | 135 |

| A.3        | Compute node schematic. Five FPGA chips are networked with               | 100 |

| 11.0       | on-board connections. Memory and peripheral components as                |     |

|            | well as communication links are placed on the board                      | 136 |

| A.4        | Prototype PCB of the compute node                                        | 137 |

| A.5        | Compute node PCB version 2                                               | 138 |

| A.6        | MPMC-based hardware design. In addition to general com-                  | 100 |

| 11.0       | ponents, customized algorithm engines are incorporated in the            |     |

|            | system for application-specific computation                              | 140 |

|            |                                                                          |     |

| B.1        | The HADES detector system                                                | 142 |

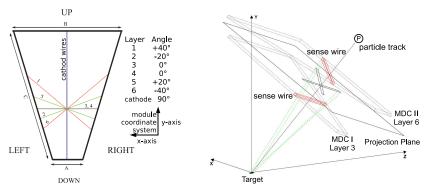

| B.2        | Particle track reconstruction in HADES MDCs                              | 143 |

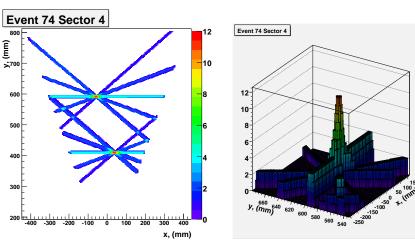

| B.3        | Track penetration points on the projection plane                         | 143 |

| B.4        | Fixed-diameter ring recognition on the RICH detector $\ \ldots \ \ldots$ | 145 |

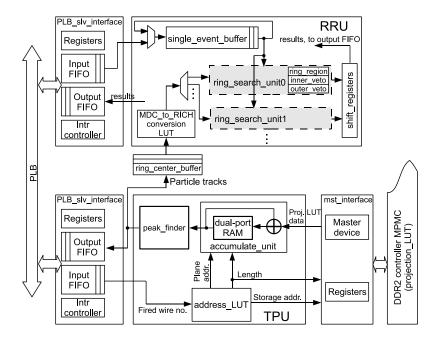

| B.5        | Hardware design of the algorithm engines                                 | 148 |

# List of Tables

| 3.1 | Resource utilization of ICAP designs on Virtex-4 FX20                      | 38  |

|-----|----------------------------------------------------------------------------|-----|

| 3.2 | Timing performance of ICAP designs                                         | 38  |

| 3.3 | Resource utilization of BRAM_pipe and DDR_pipe on Virtex-4                 |     |

|     | FX60 FPGA                                                                  | 57  |

| 3.4 | Measurement results of the pipe performance on the reconfig-               |     |

|     | urable implementation                                                      | 57  |

| 11  | D                                                                          |     |

| 4.1 | Resource utilization of the static/reconfigurable flash/SRAM               | 79  |

|     | designs                                                                    | 73  |

| 5.1 | Experimental results of the static/adaptive computing perfor-              |     |

|     | mance                                                                      | 86  |

| 5.2 | Measurement results of the context switching overhead. $\ \ldots \ \ldots$ | 87  |

| C 1 | December of the time                                                       | 06  |

| 6.1 | Resource utilization                                                       | 96  |

| 6.2 | Context switching overhead at various pipe sizes                           | 98  |

| 7.1 | Resource utilization comparison of WH-NoC and RL-NoC                       | 116 |

| 7.2 | Experimental setup of performance measurements                             |     |

|     |                                                                            |     |

| B.1 | Resource utilization of TPU and RRU                                        | 149 |

## **Abbreviations**

AHB AMBA High-performance Bus

ALICE A Large Ion Collider Experiment

AMBA Advanced Microcontroller Bus Architecture

ARM Advanced RISC Machine

ASIC Application Specific Integrated Circuit

ATCA Advanced Telecommunications Computing Architecture

ATLAS A Toroidal LHC ApparatuS

BESIII BEijing Spectrometer 3

BM Bus Macro

BRAM Block RAM

CAMAC Computer-Aided Measurement And Control

CMS Compact Muon Solenoid

CN Compute Node

CPU Central Processing Unit

xviii Abbreviations

DAQ Data AcQuisition

DDR Double Data Rate

DMA Direct Memory Access

DSP Digital Signal Processor

FIFO First-In-First-Out

FPGA Field Programmable Gate Array

FRU Field Replaceable Unit

FSM Finit State Machine

GPCPU General-Purpose Central Processing Unit

GPIO General-Purpose Input/Output

HADES High Acceptance Di-Electron Spectrometer

HDL Hardware Description Language

HW Hardware

IC Integrated Circuit

ICAP Internal Configuration Access Port

IP Intelligent Property

IPC Inter-Process Communication

IPMC Intelligent Platform Management Controller

ISE Integrated Software Environment

LE Logic Element

LHC the Large Hadron Collider

LHCb the Large Hadron Collider beauty

LUT Look-Up Table

MDC Mini Drift Chamber

MGT Multi-Gigabit Transceiver

MLND Move Logic Not Data

MOPS Mega Operations

MPMC Multi-Port Memory Controller

NI Network Interface

NoC Network-on-Chip

OPB On-chip Peripheral Bus

OS Operating System

P2P Point-to-Point

PANDA antiProton Annihilations at DArmstadt

PC Personal Computer or Physical Channel

PCB Printed Circuit Board

PIM Personality Interface Modules

PLB Processor Local Bus

PLD Programmable Logic Device

PRM Partially Reconfigurable Module

$\mathbf{x}\mathbf{x}$  Abbreviations

PRR Partially Reconfigurable Region

QoS Quality-of-Service

RICH Ring Imaging CHerenkov

RL-NoC RouterLess Network-on-Chip

RNI Resource Network Interface

RRU Ring Recognition Unit

SDF Synchronous Data Flow

SDRAM Synchronous Dynamic Random Access Memory

SIMD Single Instruction Multiple Data

SRAM Static Random Access Memory

SW Software

TDM Time-Division Multiplexing

TOF Time-Of-Flight

TPU Tracking Processing Unit

VC Virtual Channel

VCF Virtual ConFiguration

VHDL VHSIC hardware description language

VMEbus Versa Modular Eurocard bus

WH-NoC WormHole Network-on-Chip

XPS Xilinx Platform Studio

"Science is organized knowledge. Wisdom is organized life."

## Chapter 1

## Introduction

In this chapter we briefly introduce the technical background on FPGAs and reconfigurable computing. Drawbacks of using the conventional static approach to develop FPGAs are discussed. Motivated to improve the development methodology, we propose a promising solution of employing FPGA run-time reconfigurability to construct adaptive systems. In the end of the chapter, contributions of the author are clearly summarized with professional publications listed.

### 1.1 FPGA and Reconfigurable Computing

A Field-Programmable Gate Array (FPGA) is a special Integrated Circuit (IC) designed to be configurable by designers after its manufacturing, in order to obtain customized logical or arithmetic functions. It was firstly introduced by Xilinx into the commercial IC market in 1985. As the performance gap between FPGAs and ASICs decreases [1], FPGAs are playing a more and more important role in modern embedded designs. Modern FPGA products take the advantage of semiconductor technology advances, combining both programmable Logic Elements (LE) and hardcore IP blocks on the same die. They provide sufficient chip capacity and design convenience to implement a real System-on-an-FPGA, which contains microprocessors, memory controllers, hardware accelerators as well as peripheral controllers, etc. Figure 1.1 shows the capacity increment of the flagship products from the two market-dominating FPGA vendors (Xilinx and Altera) in the period from 1998

to 2009. We observe that the quantity of on-chip LEs has increased by roughly  $40\mathrm{X}$ , from  $\sim 20\mathrm{K}$  using 220 nm process in 1998 to  $\sim 800\mathrm{K}$  using 40 nm process in 2009. This chip density increment mirrors very well the famous prediction of Moore's Law.

Figure 1.1. The largest FPGA announced by Xilinx and Altera (by equivalent 4-input LEs) [2]

Programmable Logic Devices (PLD) especially FPGAs are widely employed in various application fields. Figure 1.2 demonstrates the statistics of some most significant fields in the third quarter of 2009. We see the field of communications takes the largest market share of 42%. The second largest application is industrial devices. Although contributing only a very small proportion to the market share and not even shown in the figure, scientific computing benefits also largely from FPGAs, and this application field deserves extra attention due to its special meaning for the entire human being. In this thesis work, we place our research in the application background of nuclear and particle physics experiments, which study the elementary constituents of matter and their interactions. The application background will be introduced in the next chapter.

Reconfigurable computing combines both the flexibility of software programming and the high performance of hardware acceleration by using programmable computing fabrics mainly FPGAs. The principal difference in comparison with the ordinary microprocessor computing, is the capability to make substantial changes to the data path in addition to the control flow. Actually

Figure 1.2. PLD market by end applications in the third quarter of 2009

the basic concept can be traced back to the 1960s, when Gerald Estrin's landmark paper proposed the concept of a computer made of a standard processor and an array of "reconfigurable" hardware [3] [4]. The main processor controls the behavior of the reconfigurable hardware. The latter can be tailored to perform a specific task as quickly as a dedicated piece of hardware. Unfortunately this idea was far ahead of its time in terms of needed electronics technologies. Only after the great development of configurable devices and corresponding EDA tools in the recent decade, reconfigurable computing could be really widely adopted to achieve performance benefits as well as flexible reprogrammability.

Although normally running at a much lower clock frequency, FPGA-based reconfigurable computing is believed to have a 10 - 100X accelerated performance but far lower power consumption compared to microprocessors. The development methodology on the processor software focuses on flexible control flows with limited number of Processing Elements (PE), while more concerns are placed on the data path design and optimization through parallel and pipelined approaches when developing reconfigurable hardware platforms. The on-chip memory concurrency and fine-grained computation parallelism may overcome the bottleneck existing in the computer memory system. More efficiently utilizing the expensive chip area, reconfigurable computing creates an unprecedented opportunity for orders of magnitude improvement in MOPS/dollar, MOPS/watt, and just MOPS.

In our target physics experiment applications, FPGA-based reconfigurable solutions have significant advantages to implement application-specific algorithms. They have comparatively simple control flows during data processing, and optimized data path designs can result in high performance with the on-

chip memory concurrency and fine-grained computation parallelism or pipeline support. The reprogrammability enables to change the designs to meet different experimental requirements. In addition, the ASIC production start-up cost can be saved, considering the required comparatively small quantity of chips in experimental facilities.

#### 1.2 FPGA-based System Examples

Reconfigurable computing satisfies the simultaneous demands of application performance and flexibility. In the present era when cluster-based supercomputers still dominate the fields of super computation tasks, reconfigurable computing begins showing large potential and perspective on many performance-critical areas such as realtime scientific computing. Currently commercial and academic projects are developing hardware and software to employ the raw computational power of FPGAs. Among them some platforms are augmented computer clusters with FPGAs attached to the system bus as accelerator blocks. One commercial example is the products from Cray Inc., such as XD1, XT5h series supercomputers. FPGAs are integrated in the system to embody various digital hardware designs and augment the processing capability of AMD Opteron processors [5] [6] [7]. Another instance in physics experiment applications is the ATLAS level 2 trigger [8]. Their design appears as PCI cards in commodity PCs, in which only those simple but computing-intensive steps are released to FPGAs while others remain on CPUs. One major weakness of these systems is the bandwidth bottleneck between the host microprocessor and the FPGA accelerator. In the ATLAS case, the computation work relies much on the PC and the limited bandwidth between CPUs and FPGAs via the PCI bus becomes the bottleneck when partitioning the algorithm steps to the CPU and the FPGA. There exist meanwhile standalone platforms in which FPGA units are independent on the host processors of commodity PCs. Usually in the FPGA design, less powerful embedded hardcore or softcore microprocessors are incorporated in the system, as the alternative of PC processors to conduct controls or HW/SW coprocessing tasks. For instance the Dini Group products [9] combine multiple FPGA chips through on-board interconnections and target mainly logic emulation and ASIC verification applications. In addition the Berkeley Emulation Engine (BEE) represents powerful and scalable platforms for large scale data processing [10] [11] [12]. Its various product generations employ different communication standards, such as Infiniband, Gigabit Ethernet, or PCI Express, etc., to network the Printed Circuit Boards (PCB) for system scaling. The

1.3. Motivation 7

recent COPACOBANA [13] and the CUBE [14] projects use plentiful interconnected FPGAs to run cryptanalytical algorithms. Specific to their application requirements, the hardware design suits to solve parallel computation-hungry problems partitioned into many FPGA chips, but features small memory bandwidth and capacity as well as low inter-chip communication requirements.

According to the computation and communication requirements in our target physics applications, we have designed a hierarchical and scalable FPGA-based computation platform that is optimized to interface with other experimental devices and conducts the large-scale data processing work. Details on the hardware and FPGA development may be referred to in Appendix A.

#### 1.3 Motivation

Despite large advances on the density and work frequency, the chip area utilization efficiency and the system clock speed of FPGAs are still low compared to the gate-based logic implementation on ASICs. On the FPGA, Look-Up Table (LUT) units are employed instead to construct combinational logic, leading to larger area occupation on the die and slower work frequency than elementary gates. In [15], the authors have measured FPGA designs to be 35X larger in area and 3X slower in speed than a standard cell ASIC flow, both using 90-nm technology. In [16], a 12 year old Pentium design was ported on a Xilinx Virtex-4 FPGA. A 3X slower system speed (25 MHz vs. 75 MHz) is still observed, even though the FPGA uses a recent 90-nm technology while the original ASICs were 600-nm. The speed and area utilization gap between FPGAs and ASICs has also been differently quantified in [17] and [18] for various designs. We see that FPGA programmable resources are still comparatively expensive. Efficient resource management and utilization remain to be a challenge especially for the applications with simultaneous high-performance and low cost requirements.

From another point of view, design complexity especially in massive processing systems is increasing rapidly and becoming unmanageable. Imagining an FPGA cluster consisting of hundreds of interconnected FPGAs, heterogeneous functional modules have to be selected and integrated in system designs. Bitstream files must be downloaded into the correct FPGA chip. The design management work is annoying and error-prone if it is done by mentally overloaded designers.

The conventional approach to develop FPGAs is static: The entire system is partitioned into tasks and implemented as hardware components. Design components are managed and assembled by designers during their development

period. They are statically mapped on the FPGA fabric, being instantiated throughout the system operation time. The functionalities normally do not change when the design is still in operation. Drawbacks exist in the static development approach, as itemized as follows:

- Design management complexity. Designs are managed by designers offline. The human being must face the complexity and error possibilities, especially in heterogeneous massive systems consisting of large quantity of FPGAs.

- 2. Resource utilization inefficiency. With respect to some design modules which may only occasionally function or do not function simultaneously at all, it is a large waste to respectively allocate them on-chip resources. More utilized resources not only lead to higher static power consumption, but also may result in extra hardware upgrade budget if new functionalities are expected but the chip is already fully occupied.

- 3. **Incapability of run-time maintenance.** Static designs do not possess the capability of online maintenance. In order to modify or upgrade the firmware, the entire system may have to be completely stopped. This might not be permitted at all or very expensive in some situations, such as in the physics experiments.

As a promising solution, adaptive computing [19] [20] is the paradigm in which computation tasks may vary and adapt to system status or ambient conditions during run-time. Its self-awareness distinguishes itself from existing computational models, which are mostly procedural and simply a collection of static functional components. Typically an adaptive system keeps aware the context and changes its processing behavior according to trigger events such as workload variations, computation interest switching, or environmental situations. As a consequence, benefits including more efficient utilization of computation resources, lower power consumption or multitasking on limited resources may be obtained by dynamically modifying the system design or adjusting important parameters. One major prerequisite of adaptive computing, is the reprogrammability of the computer systems: On General-Purpose microprocessors (GPCPU), different computation tasks can be easily accomplished by conditionally branching to different instructions. Nevertheless hardware logic is not straightforwardly adaptable in contrast to the software computation, in which the computation resource of CPU cores is intrinsically time-shared among various tasks. Thanks to the newly emerged Partial Reconfiguration (PR) technology, which offers the possibility to dynamically change part of the FPGA design without stopping the remaining system. The PR feature provides much convenience in realizing adaptive computing scenarios, in which basic functions are to be maintained while specific algorithms or algorithm steps can be freely adjusted. It is the PR technology that firstly introduces the concept of Time-Division Multiplexing (TDM) into FPGA resource managements. It leads to the benefits of more efficient resource utilization, shorter reconfiguration time, as well as lower static power dissipation [21] [22] [23].

#### 1.4 Thesis Outline and Author's Contributions

The thesis is constructed into chapters listed as follows:

- Chapter 1: In this chapter we recall the readers with related technical background on FPGAs and reconfigurable computing. We analyze the main-stream development approach in existence and raise the necessity to improve the design methodology with self-adaptation features. In the end of the chapter, relevant publications on which this thesis is based are listed.

- Chapter 2: Since we target a very special application in high-energy physics experiments, it is necessary to reveal a picture of their particularities to the readers who are not familiar with this interdisciplinary field. Hence we do a brief application introduction in this chapter, and the knowledge on the application background also helps to understand the motivation of the research work.

- Chapter 3: In this chapter we present the proposed design framework for adaptive computing based on FPGA run-time reconfigurability. The framework is comprehensive and key issues are systematically discussed in different hardware/software layers. These aspects should be taken into account when practically building an adaptive design on the FPGA.

- Chapter 4: Right after the discussion on the design framework, we employ a case study to verify the concept: Two types of memory controllers time-share the same reconfigurable slot and they are adaptively loaded to work according to different memory addressing requirements. This case study reveals general benefits for FPGA-based embedded designs, on the basis of accomplishing all the expected functionalities in the system.

- Chapter 5: This chapter focuses on the performance analysis of adaptive multi-stream processing. Correlated multi-streaming acts as the

fundamental model of our target applications in high-energy physics experiments. Theoretical analysis and experimental results on the model show the potential merits of applying the self-adaptation concept in data stream processing scenarios.

- Chapter 6: Combined with the model analysis in the previous chapter, we apply the adaptively reconfigurable framework to the case study of a real application for particle recognition computation. Two pattern recognition algorithms are alternately configured to process their respective data streams, with their synchronization (correlation) requirement automatically and optimally guaranteed. Experimental results demonstrate practical design benefits.

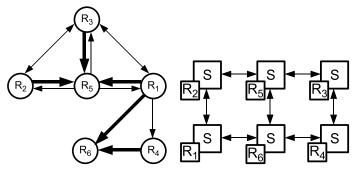

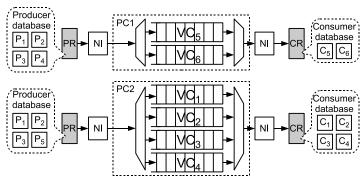

- Chapter 7: Taking advantage of the run-time reconfigurability, we introduce a novel on-FPGA interconnection microarchitecture called Router-Less Network-on-Chip (RL-NoC) in this chapter. From the principle point of view, it significantly distinguishes itself from the conventional interconnection approaches such as buses, crossbars or NoCs. RL-NoC features many advantages in the aspects of design complexity, resource utilization, power consumption, operation frequency, etc. Meanwhile a comparable or even superior throughput performance can be achieved in comparison with a canonical wormhole NoC.

- Chapter 8: In this chapter we conclude the thesis. We summarize the advantages of the discussed design framework for adaptive computing as application references, and raise open issues for the future work in this field.

- Appendix A: In this appendix chapter, related engineering work is concerned on the FPGA-based reconfigurable platform design. This large-scale system aims at our physics applications of data acquisition (DAQ) and triggering in experiments. Moreover, the FPGA board works as the experiment platform on which researches have been carried out.

- Appendix B: The application-specific computation is introduced in this

appendix chapter, specifically MDC particle track reconstruction and

RICH Cherenkov ring recognition. This part consists of physics background in the detector system, algorithm description, as well as hardware implementations on FPGAs. The hardware implementation of both

algorithms behaves as the basis of the second case study discussed in

Chapter 6.

The author's publications are classified into three areas: system design and development, algorithm implementation, and adaptive computing. The last topic represents the author's main research contribution and it runs throughout the content of this thesis. The former two topics are application related and discussed in the appendices. The publications are itemized as follows:

#### Adaptive computing:

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "A Hardware/Software Design Framework for FPGA-based Self-aware Adaptive Computing", under submission. [24]

- 2. Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "A Lightweight Routerless Network-on-Chip Infrastructure using FPGA Dynamic Reconfigurability", under submission. [25]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "Adaptively Reconfigurable Controller for the Flash Memory", Book of Flash Memory, invited book chapter, InTech, ISBN: 978-953-307-272-2, 2011. [26]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "Inter-Process Communications using Pipes in FPGA-based Adaptive Computing", In Proceeding of the IEEE Computer Society Annual Symposium on VLSI, Lixouri Kefalonia, Greece, Jul. 2010. [27]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "Reducing FPGA Reconfiguration Time Overhead using Virtual Configurations", In Proceeding of the International Workshop on Reconfigurable Communication Centric System-on-Chips, Karlsruhe, Germany, May 2010. [28]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "FPGA-based Adaptive Computing Architecture for Correlated Multi-stream Processing", In Proceeding of the Design, Automation and Test in Europe conference, Dresden, Germany, Mar. 2010. [29]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, Shuo Yang and Axel Jantsch, "A Reconfigurable Design Framework for FPGA Adaptive Computing", In Proceeding of the International Conference on ReConFigurable Computing and FPGAs, Cancun, Mexico, Dec. 2009. [30]

- 8. Ming Liu, Wolfgang Kuehn, Zhonghai Lu, and Axel Jantsch, "Run-time Partial Reconfiguration Speed Investigation and Architectural Design

Space Exploration", In Proceeding of the International Conference on Field Programmable Logic and Applications, Prague, Czech Republic, Aug. 2009. [31]

#### System design and development:

- Ming Liu, Wolfgang Kuehn, Soeren Lange, Shuo Yang, Johannes Roskoss, Zhonghai Lu, Axel Jantsch, Qiang Wang, Hao Xu, Dapeng Jin, and Zhenan Liu, "A High-end Reconfigurable Computation Platform for Nuclear and Particle Physics Experiments", Computing in Science and Engineering, vol. 13, no. 2, pp. 52-63, Mar./Apr. 2011. [32]

- 10. Qiang Wang, Axel Jantsch, Dapeng Jin, Andreas Kopp, Wolfgang Kuehn, Johannes Lang, Soeren Lange, Lu Li, Ming Liu, Zhenan Liu, Zhonghai Lu, David Muenchow, Johannes Roskoss, and Hao Xu, "Hardware/Software Co-design of an ATCA-based Computation Platform for Data Acquisition and Triggering", In Proceeding of the IEEE NPSS Real Time Conference, Beijing, China, May 2009. [33]

- 11. Ming Liu, Johannes Lang, Shuo Yang, Tiago Perez, Wolfgang Kuehn, Hao Xu, Dapeng Jin, Qiang Wang, Lu Li, Zhenan Liu, Zhonghai Lu, and Axel Jantsch, "ATCA-based Computation Platform for Data Acquisition and Triggering in Particle Physics Experiments", In Proceeding of the International Conference on Field Programmable Logic and Applications 2008, Heidelberg, Germany, Sep. 2008. [34]

- 12. Ming Liu, Wolfgang Kuehn, Zhonghai Lu, Axel Jantsch, Shuo Yang, Tiago Perez, and Zhenan Liu, "Hardware/Software Co-design of a General-Purpose Computation Platform in Particle Physics", In Proceeding of the IEEE International Conference on Field Programmable Technology, Kitakyushu, Kokurakita, Japan, Dec. 2007. [35]

- 13. Wolfgang Kuehn, Camilla Gilardi, Daniel Kirschner, Johannes Lang, Soeren Lange, Ming Liu, Tiago Perez, Lars Schmitt, Dapeng Jin, Lu Li, Zhenan Liu, Yunpeng Lu, Qiang Wang, Shujun Wei, Hao Xu, Dixin Zhao, Krzysztof Korcyl, Jacek Tomasz Otwinowski, Piotr Salabura, Igor Konorov, and Alexander Mann, "FPGA Based Compute Nodes for the PANDA Experiment at FAIR", In Proceeding of the NPSS Real Time Conference, Batavia, USA, Apr. 2007. [36]

Tiago Perez, Camilla Gilardi, Ming Liu, and Shuo Yang, "A FPGA-based Compute Node for the PANDA Data Acquisition and Trigger System", In Proceeding of the International Winter Meeting on Nuclear Physics, Bormio, Italy, Apr. 2007. [37]

#### Algorithm implementation:

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "FPGA-based Particle Recognition in the HADES Experiment", *IEEE Design and Test of Computers*, special issue on Design Methods and Tools for FPGA-Based Acceleration of Scientific Computing, Jul./Aug. 2011 (accepted). [38]

- Ming Liu, Zhonghai Lu, Wolfgang Kuehn, and Axel Jantsch, "FPGA-based Cherenkov Ring Recognition in Nuclear and Particle Physics Experiments", In Proceeding of the International Symposium on Applied Reconfigurable Computing, Belfast, United Kingdom, Mar. 2011. [39]

- 17. Ming Liu, Axel Jantsch, Dapeng Jin, A. Kopp, Wolfgang Kuehn, J. Lang, L. Li, Soeren Lange, Zhenan Liu, Zhonghai Lu, D. Muenchow, V. Penchenov, Johannes Roskoss, S. Spataro, Qiang Wang, and Hao Xu, "Trigger Algorithm Development on FPGA-based Compute Node", In Proceeding of the IEEE NPSS Real Time Conference, Beijing, China, May 2009. [40]

- 18. Ming Liu, Wolfgang Kuehn, Zhonghai Lu, and Axel Jantsch, "System-on-an-FPGA Design for Real-time Particle Track Recognition and Reconstruction in Physics Experiments", In Proceeding of the EUROMI-CRO Conference on Digital System Design, Parma, Italy, Sep. 2008. [41]

Other publications which are not concerned in this thesis include:

- 19. Daniel Georg Kirschner, Geydar Agakishiev, Ming Liu, Tiago Perez, Wolfgang Kuehn, Vladimir Pechenov, and Stefano Spataro, "Level 3 Trigger Algorithm and Hardware Platform for the HADES Experiment", Nuclear Instruments and Methods in Physics Research A, Volume 598, Issue 2, pp. 598 604, 2008. [42]

- Zhonghai Lu, Ming Liu, and Axel Jantsch, "Layered Switching for Networks on Chip", In Proceeding of the Design Automation Conference, San Diego, USA, Jun. 2007. [43]

# "Thinking is more interesting than knowing, but less interesting than looking."

Johann Wolfgang von Goethe (German Playwright, Poet, Novelist and Dramatist, 1749 - 1832 A.D.)

### Chapter 2

# **Application Background**

This chapter concerns the necessary introduction of our target application: data acquisition and triggering in nuclear and particle physics experiments. This special application acts as a representative of large-scale computing in scientific researches, which benefit from modern semiconductor and FPGA technologies. It differs significantly from the common embedded designs such as consumer electronics or mobile devices, and therefore deserves a brief overview for the readers.

#### 2.1 Nuclear and Particle Physics Experiments

Nuclear and particle physics is a branch of physics that studies the elementary constituents of matter and the interactions between them. It is also called high-energy physics because many elementary particles do not occur under normal circumstances in nature, but can be created and detected during energetic collisions of other particles, as is done in particle colliders. In the experiments, beam particles are accelerated to a velocity approaching to the speed of light and then collide with target particles. Modern nuclear and particle physics experiments, for example HADES [44] and PANDA [45] at GSI Germany, BESIII [46] at IHEP China, ATLAS, CMS, LHCb, ALICE at the LHC [47] at CERN Switzerland, achieve their goals by studying the emission direction, the energy, and the mass of the produced particles when the beam hits the target. In the experimental facilities, different kinds of detectors are adopted to generate raw data which are used to calculate and analyze the

characteristics of emitted particles after the collision. Figure 2.1 shows the exploded view of the HADES detector system as an example.

Figure 2.1. Dismounted view of the HADES detector system

In high-energy physics, one "event" corresponds to a single interaction of a beam particle with a target particle. It consists of sub-events which typically represent the information from individual detector sub-systems, such as RICH (Ring Image CHerenkov), MDCs (Mini Drift Chamber), TOF (Time-Of-Flight), etc., as shown in Figure 2.1. Figure 2.2 demonstrates an example event structure consisting of sub-events from various detectors. The event data are to be filtered and recorded during experiments. Afterwards physicists will extensively analyze the events to search for interesting ones such as new types of particles.

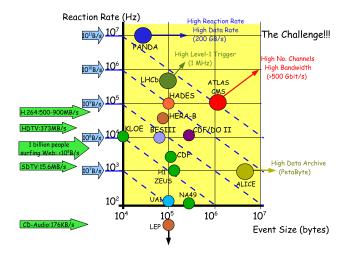

The detector system in experimental facilities has commonly more than  $10^5$  signal channels, and the delivered data rate which is the product of the event size and the reaction rate might be a scary number (e.g. PANDA, the reaction rate of 10 - 20 MHz and the data rate of more than 200 GBytes/s). Compared to the bandwidth needed by some other applications [48], Figure 2.3 lists some experiments by their event sizes and reaction rates. We see that their data rates range from  $10^7$  up to  $10^{11}$  Bytes/s, which are too large for the disk or tape storage to entirely record the data throughout the experiment time lasting for months. Furthermore, the supercomputers would take forever to

Figure 2.2. Event structure consisting of sub-events from different detectors

process all the data during offline analysis. Among the generated events, only a rare fraction with particular physics contents is of interest for the physicists. Such events might occur only once within one million interactions. Therefore it is essential to realize an efficient on-line data acquisition (DAQ) and trigger system which processes the sub-events coming from detectors and reduces the data rate by several orders of magnitude by means of rejecting the background.

Figure 2.3. Experiments with different event sizes and reaction rates

#### 2.2 DAQ and Trigger System

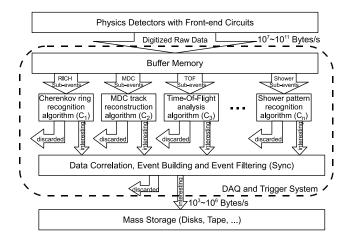

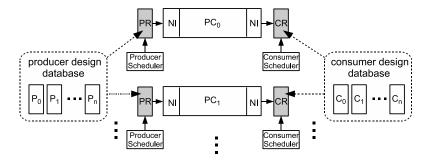

In the contemporary facilities, pattern recognition algorithms [49] [50] [51] such as Cherenkov ring recognition, particle track reconstruction, Time-Of-Flight (TOF) processing, Shower recognition, are implemented as sophisticated criteria according to detector categories. Only the sub-events which possess expected patterns generated by certain types of particles and could be successfully correlated among different detectors, trigger a positive decision and are encapsulated in a pre-defined event structure for mass storage and further offline analysis. Others will be discarded on the fly in order to reduce the data rate. Figure 2.4 demonstrates a sample multi-streaming data flow in the experiments, which will be later modeled and analyzed in Chapter 5.

Figure 2.4. Multi-streaming data flow in DAQ and trigger systems

As an alternative approach of the traditional PC farm based pure software computation, modular approaches with commercial bus systems, such as VMEbus, FASTbus, and CAMAC, can be utilized to construct DAQ and trigger systems for high-energy physics experiments [52] [53] [54] [55]. These systems which usually contain programmable devices like FPGAs or DSPs may interface to PC clusters for hardware/software hybrid processing. An instance is the NA48 experiment [56], in which FPGAs are used to build wire hit coordinates for the pion particle  $(\pi)$  track reconstruction computation, and the trigger core algorithm is implemented on interconnected Digital Signal Processors (DSP). The customized hardware boards are installed on 4 VME crates.

One SUN workstation remotely monitors the entire system through a private Ethernet network. There is an additional SPARC VME SBC computer board in each crate running Unix to control the system. However due to the largely increased data rate generated by the detector systems in modern experiments, the obsolete bus-based technologies cannot meet the increasing experimental requirements any longer. The time-multiplexing nature of the system bus not only deteriorates the data exchanging efficiency among algorithms residing on different pluggable modules, but also restricts the flexibility to partition complex algorithms. Nowadays the networking and switching technologies make it efficient to construct large-scale systems for parallel and pipelined processing. In addition, great development on FPGAs provides the practicability to release some complex algorithms, which were conventionally implemented as software on workstations or embedded processors/DSPs, into the FPGA fabric for high-performance hardware processing. For example in [57], the authors utilize FPGAs to implement the Compact Muon Solenoid (CMS) trigger of the Large Hadron Collider (LHC) particle accelerator at CERN.

As a general-purpose solution for data acquisition and trigger applications in various physics experiments, specifically the HADES and BESIII upgrade and the PANDA construction projects, we have designed and developed a computation platform consisting of interconnected nodes based on the Advanced Telecommunications Computing Architecture (ATCA) standard [58]. To simultaneously satisfy various algorithm partition and correlation requirements for current or future experiments, the full-mesh Point-to-Point (P2P) backplane has been chosen to interconnect multiple FPGA-based Compute Nodes (CN) for massive parallel processing. External channels including optical links as well as Gigabit Ethernet, are engaged in receiving sub-events from detectors and forwarding processing results to the PC farm for mass storage and offline analysis. Internal hierarchical interconnections, including the interchassis optical link and Ethernet switching, inter-board full-mesh backplane connections, and on-board FPGA I/O channels, are utilized to partition and distribute algorithms or algorithm steps for parallel/pipelined trigger processing and correlation. In the ATCA crate, CNs appear as Field Replaceable Units (FRU), which are interconnected with each other by backplane channels. On each CN, five Xilinx Virtex-4 FX60 FPGAs are placed on board and mutually interconnected by General-Purpose I/O (GPIO) buses as well as RocketIO serial links. Four FPGAs work as algorithm processor nodes, and the fifth one as a switch interfacing to the backplane. Detailed architectural description on the ATCA-based computation platform and the CN design will be separately discussed in Appendix A. Trigger algorithm implementations on the FPGA can be found in Appendix B.

#### 2.3 Design Challenges

Design and development of DAQ and trigger systems in high-energy physics experiments feature different requirements from other common applications, such as consumer electronics or mobile devices. Design particularities and challenges are partly summarized in the following aspects:

- Large system scale. The DAQ and trigger system designs typically feature an enormous scale. As we mentioned in the first section of this chapter, the raw data rate generated by particle detectors may reach up to several hundreds of GBytes/s. The number of links used to dump the data into the system can easily reach the order of magnitude of hundreds. With respect to the computation power, it may also contain hundreds of high-end FPGA chips in order to distribute algorithm components for concurrent data processing.

- Development difficulty. Diverse trigger algorithms are to be implemented and optimized, corresponding to the combinational detector system adopted to investigate various particle characteristics. These algorithms often concern sophisticated principles and their implementations must satisfy certain performance requirements.

- Design management complexity. For such a large-scale system, the design management work is not negligible. How to reasonably partition computation tasks, to efficiently organize the interconnection network of task nodes, to map hardware implementations on different FPGA chips, and to manage design and bitstream files for hundreds of FPGAs with online and remote reconfiguration requirements, raise extra complexity to the system developers.

- Run-time maintenance requirement. In some circumstances, the system is expected to be online maintainable with partial functionalities kept running. A complete stop may delay the experimentation progress, and the financial cost introduced by the delay cannot be simply ignored. (With respect to the experimental facilities, even the power cost itself is an enormous number.)

- Expensive hardware cost. Due to the large scale of the system, hardware cost becomes a very critical issue. Optimized designs which may fully exploit the hardware resources, can actually reduce the hardware cost from another standpoint.

• Long development cycle. A complete DAQ and trigger system design typically lasts for 5 to 10 years or even longer.

We understand that to construct a complex DAQ and trigger system for high-energy physics applications can largely benefit from an optimal design and development methodology on FPGAs. The modern FPGA partial reconfiguration technology provides a good tool to address some dilemmas generated by the conventional static approach. Therefore we investigate the adaptive development methodology in the context of physics applications. Detailed discussion in various aspects goes in the following chapters of this thesis.

# "Learning without thought is labor lost; thought without learning is perilous."

Confucius

(Chinese educator, philosopher, and political theorist, 551 - 479 B.C.)

## Chapter 3

# Design Framework for Adaptive Computing

In this chapter we present a comprehensive and practical design framework for adaptive computing based on FPGA run-time reconfigurability. Several design key issues are systematically discussed in different hardware/software layers, concerning hardware architecture, run-time reconfiguration technology, OS and device drivers, hardware process scheduler, context switching as well as inter-process communications. All are the aspects which should be taken into account when practically building an adaptive system on FPGAs. The themes of this chapter cover paper [24], [27], [28], [30], and [31] listed in Section 1.4.

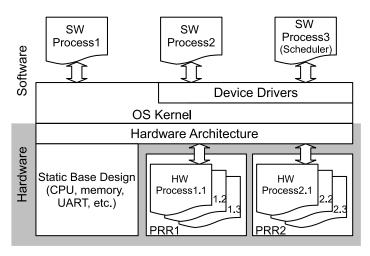

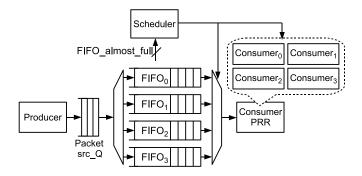

The modular design concept frequently adopted in static designs applies also to run-time reconfigurable designs on FPGAs. In adaptive computing, the entire system is partitioned and different tasks are to be individually implemented as functional modules. Analogous to software processes running on top of Operating Systems (OS) and competing for the CPU time, each functional module can be regarded as a hardware process which is to be loaded into reconfigurable slots on the FPGA rather than GPCPUs. Multiple hardware processes may share the same programmable resources and be scheduled to work according to certain disciplines on the awareness of computation requirements. Context switching happens when the current hardware process of a

task is leaving the reconfigurable slot (being overwritten) and a new task is to be loaded to start working. All these key issues in the adaptive computing framework are classified into and addressed within certain layers in hardware or software. Figure 3.1 demonstrates the layered hardware/software architecture and details in different aspects will be presented in the following sections respectively.

Figure 3.1. Hardware/software layers of the adaptive system

#### 3.1 Related Work

Run-time partially reconfigurable designs become practically feasible only in the recent years, as the official technical support was announced by FPGA vendors. The PR technology is foreseen to be more and more widely used for addressing various design challenges, such as multitasking on limited resources, power reduction, cost reduction, etc. However to our best knowledge, the design framework for adaptively changeable functional modules with context-awareness is not yet well regulated in various hardware/software layers. Contributions exist concerning specific aspects of run-time reconfigurable designs.

Resource management on reconfigurable devices is a key issue of adaptive computing. In [59], a resource allocation model is presented for load-balancing

3.1. Related Work 29

processing of multitasks. The complicated hardware architecture consisting of hierarchical Upper Management Units (UMU), Management Units (MU), Processing Units (PU) and Re-ordering Units (RU), makes it difficult and impractical for implementation. In [60], the single processor scheduling algorithm is investigated and applied to task hardware module reconfigurations. The proposed Earliest Due Date (EDD) model for synchronous tasks and the Earliest Deadline First (EDF) model for asynchronous tasks can improve the module response time when multiple designs are being alternatively loaded into multiple reconfigurable slots. Additional scheduling mechanisms and task management studies can be found in [61], [62] and [63]. However, most of the above cited investigations concentrate only on the modeling level and do not take into account practical constraints in reconfigurable designs. In [64], a practical hardware/software environment is implemented and tested to manage hardware processes on FPGAs, with the help of a modified Linux kernel called BORPH. The authors' main contribution is to enhance the OS kernel to support hardware processes and schedule them altogether with normal software processes. Nevertheless the modification work in the OS kernel space is error prone and makes the reconfigurable design dependent on the customized OS. It generates many difficulties to port the schedulable system onto different platforms.

In addition, contributions on the PR relevant issues have been reported in some other aspects: In [65], [66] and [67], run-time reconfiguration speed has been investigated and optimized, enabling practical PR designs with low reconfiguration time overhead. In [68], the authors present the approach to save and restore the hardware context of reconfigurable modules, by parsing the FPGA bitstream and extracting or recovering corresponding information. In order to interface dynamically swappable IP modules with the static system, the authors of [69] propose three wrapper designs which feature a buffer for reading out or restoring the context data of reconfigurable modules. The authors of [70] and [71] analyze the signal routing dilemmas in reconfigurable designs, and optimize communications among relocatable modules simultaneously residing in different configuration slots with a set of inter-module communication paradigms. Unfortunately the challenge of communications among hardware processes that are time-multiplexed in the same reconfigurable slot in sequence are not concerned in their work.

#### 3.2 Overview of FPGA PR Technology

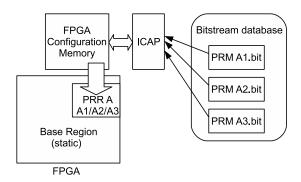

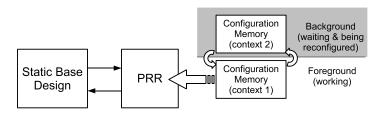

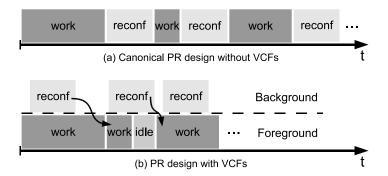

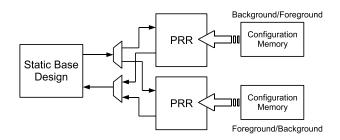

Modern FPGAs (e.g. Xilinx Virtex-4, 5, and 6 FPGAs) offer the partial reconfiguration capability to dynamically change part of the design without stopping the remaining system. This feature enables alternate utilization of on-FPGA programmable resources, therefore resulting in large benefits such as more efficient resource utilization and less static power dissipation [21]. Figure 3.2 illustrates a reconfigurable design example on Xilinx FPGAs: In the design procedure, a Partially Reconfigurable Region (PRR) A is reserved in the overall design layout mapped on the FPGA. Various functional Partially Reconfigurable Modules (PRM) are individually implemented within this region, and their respective partial bitstreams are generated and collectively initialized in a design database residing in memory devices in the system. During system run-time, various bitstreams can be dynamically loaded into the FPGA configuration memory by its controller named Internal Configuration Access Port (ICAP). With a new module bitstream overwriting the original one in the FPGA configuration memory, the PRR is loaded with the new module and the circuit functions according to its concrete design. In the dynamic reconfiguration process, the PRR has to stop working for a short time (reconfiguration overhead) until the new module is completely loaded. The static portion of the system will not be disturbed at all.

Figure 3.2. Partially reconfigurable design on Xilinx FPGAs

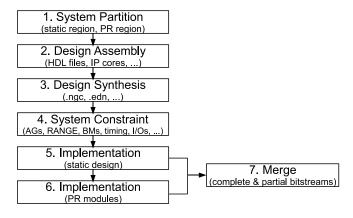

The PR technology is coupled very closely to the underlying framework of the FPGA chip itself. We use the Xilinx FPGAs to explain the PR design flow as illustrated in Figure 3.3: The design begins from partitioning the system between the static base design and the reconfigurable part. Usually basic hardware infrastructures that expect continuous work and do not want to be unloaded or replaced during the operation are classfied into the static category, such as the system processor or the memory controller. The partially reconfigurable part delegates those modules with dynamically swapping needs in the PR region. All the modular designs including PRMs are assembled to form an entire system. After synthesis, netlist files are generated for all the modules as well as the top-level system. The netlists serve as input files to the FPGA implementation. Before implementation, the Area Group (AG) constraints must be defined to prevent the logic in PRMs from being merged with the one in the base design. Each PRR will be only restricted in the area defined by the RANGE constraints. Then after the following individual implementation of the base system and PR modules, the final step in the design flow is to merge them and create both a complete bitstream (with default PR modules equipped) and partial bitstreams for PR modules. Hence, run-time reconfiguration will be initiated when a partial bitstream is loaded into the FPGA configuration memory and overwrites the corresponding segment.

Figure 3.3. Xilinx PR design flow

#### 3.3 Hardware Architecture

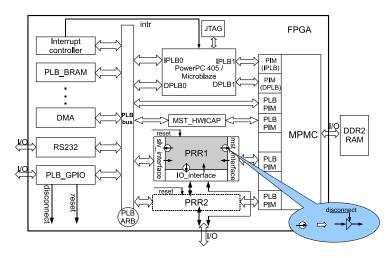

A dynamically reconfigurable design may consist of a general-purpose computer system and application-customized functional modules, as shown in Figure 3.4 for a system on a Xilinx Virtex-4 FPGA. Existing commercial IP cores can be exploited to quickly construct the general computer design. The

application-specific tasks such as algorithm accelerators feature the largest design challenges, and should be customized and optimized according to specific requirements. They are to be integrated in the system design to communicate with other components, specifically the host processor, the memory or some peripherals. In order to shorten the development period, the general computer design may be largely retained for different applications. The designers concentrate on the application-specific functionalities, customizing and optimizing the required modules.

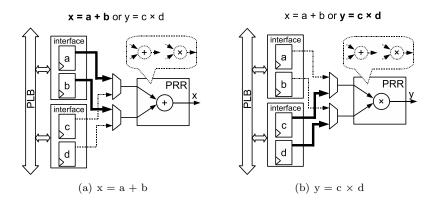

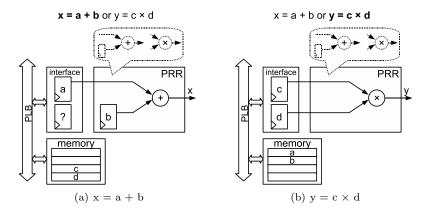

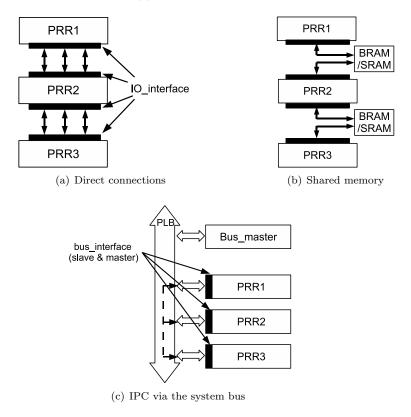

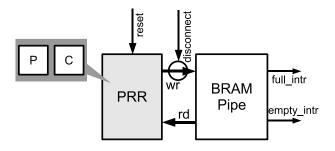

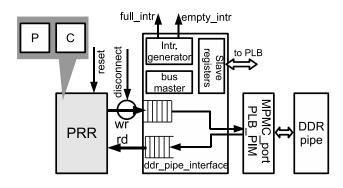

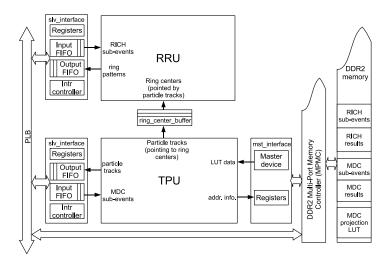

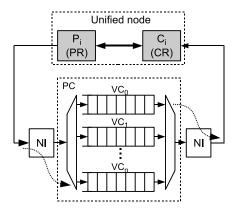

Figure 3.4. The hardware infrastructure of the PR system

In FPGA-based adaptive computing, PRRs or reconfigurable slots are reserved in the system for being dynamically equipped with different functional modules. In Figure 3.4 we show two PRRs to demonstrate the principle. When incorporated in the system design, PRMs connect to the static base design, specifically the PLB bus for receiving controls from the processor, the Multi-Port Memory Controller (MPMC) for efficiently accessing the system memory, and I/O buffers for addressing external devices. Respective interface wrappers (slave or slv, master or mst, and IO\_interface) provide standard ports to connect PRMs to the base design. Direct I/O channels may also exist among various PRRs. Noting that the output signals from a PRM may unpredictably toogle during ongoing reconfiguration, "disconnect" logic (illustrated in the callout frame in Figure 3.4) is therefore required to be inserted to disable PRM outputs and isolate the unsteady signal states for the base design from

being interfered. Furthermore, a dedicated "reset" signal aims to solely reset the newly loaded module after each partial reconfiguration. Both the "disconnect" and the separate "reset" signals can be driven by a register-accessible General-Purpose I/O (GPIO) core under the control of the host processor.

In the previous Xilinx Partial Reconfiguration Early Access design flow [72], a special type of component called Bus Macro (BM) must be instantiated in the interface designs, straddling the PR region and the static design to lock the implementation routing between them. This is the particular treatment on the communication channels between the static and the dynamically reconfigurable regions. However in the new PR design flow [73], BMs are no longer needed and partition I/Os are automatically managed by the development software tool.

One significant advantage of this hardware architecture, is that it conforms to the standard Xilinx design tradition of embedded systems: The application-specific tasks are implemented into IP cores. They are wrapped by interface blocks and incorporated in the bus-based system design. Normal static designs can be easily converted into a PR system by extracting task components, combining common interfaces, and sharing the same programmable resources in a preserved PR region. Little special consideration is needed to construct a PR system on the basis of conventional static designs.

# 3.4 Run-time Reconfiguration Technical Support

#### 3.4.1 ICAP Designs

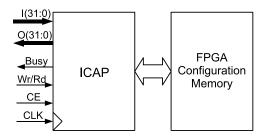

The ICAP primitive is the hardwired FPGA logic by which the bitstream can be downloaded into the configuration memory. As shown in Figure 3.5, ICAP interfaces to the configuration memory and provides parallel access ports to programmable resources. During the system run-time, a master device (typically an embedded microprocessor) may transmit partial reconfiguration bitstreams from the storage device to ICAP to accomplish the reconfiguration process. The complete ICAP design, in which the ICAP primitive is instantiated, interfaces to the system interconnection fabric to communicate with the processor and memories.

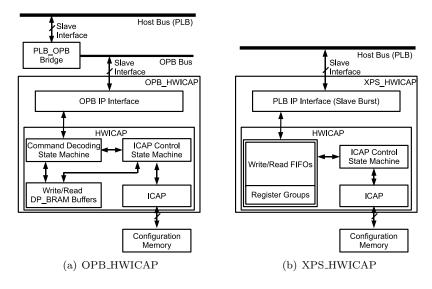

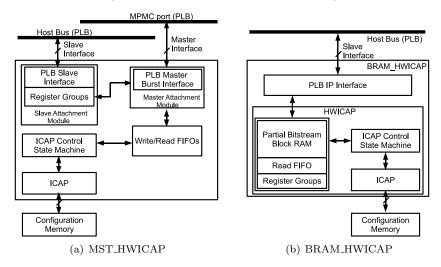

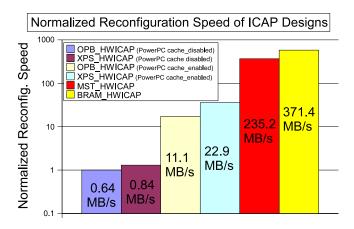

As the Xilinx reference designs for PR, the structures of OPB\_HWICAP [74] and XPS\_HWICAP [75] are demonstrated respectively in Figure 3.6(a) and Figure 3.6(b). The OPB\_HWICAP core was previously designed for the low-performance OPB bus. To link the OPB core to the system PLB, a bridge

Figure 3.5. The ICAP primitive on Xilinx FPGAs