of Technology

# Performance Analysis of Application-Specific Multicore Systems on Chip

Iyad Al Khatib

A thesis submitted to The Royal Institute of Technology in partial fulfillment of the requirements for the degree of Doctor of Technology

June 13, 2008

Department of Electronic, Computer, and Software Systems (ECS) School of Information and Communication Technology (ICT) Royal Institute of Technology (KTH)

Stockholm, Sweden

#### Al Khatib, Iyad Performance Analysis of Application-Specific Multicore Systems on Chip

Doctoral Thesis in Electronic and Computer Systems Department of Electronic, Computer, and Software Systems (ECS) School of Information and Communication Technology (ICT) Royal Institute of Technology (KTH)

TRITA-ICT/ECS AVH 08:06 ISSN 1653-6363 ISRN KTH/ICT/ECS/ AVH-08/06--SE ISBN 978-91-7178-960-0

KTH/ICT/ECS: Electronic, Computer, and Software Systems Royal Institute of Technology Isafjordsgatan 39 P.O. Box Forum 120 SE-164 40 Kista Sweden

Copyright © Iyad Al Khatib, June 13, 2008

ii

### ABSTRACT

The last two decades have witnessed the birth of revolutionary technologies in data communications including wireless technologies, System on Chip (SoC), Multi Processor SoC (MPSoC), Network on Chip (NoC), and more. At the same time we have witnessed that performance does not always keep pace with expectations in many services like multimedia services and biomedical applications. Moreover, the IT market has suffered from some crashes. Hence, this triggered us to think of making use of available technologies and developing new ones so that the performance level is suitable for given applications and services. In the medical field, from a statistical viewpoint, the biggest diseases in number of deaths are heart diseases, namely Cardiovascular Disease (CVD) and Stroke. The application with the largest market for CVD is the electrocardiogram (ECG/EKG) analysis. According to the World Health Organization (WHO) report in 2003, 29.2% of global deaths are due to CVD and Stroke, half of which could be prevented if there was proper monitoring. We found in the new advance in microelectronics, NoC, SoC, and MPSoC, a chance of a solution for such a big problem. We look at the communication technologies, wireless networks, and MPSoC and realize that many projects can be founded, and they may affect people's lives positively, as for example, curing people more rapidly, as well as homecare of such large scale diseases. These projects have a medical impact as well as economic and social impacts. The intention is to use performance analysis of interconnected microelectronic systems and combine it with MPSoC and NoC technologies in order to evolve to new systems on chip that may make a difference. Technically, we aim at rendering more computations in less time, on a chip with smaller volume, and with less expense. The performance demand and the vision of having a market success, i.e. contributing to lower healthcare costs, pose many challenges on the hardware/software co-design to meet these goals. This calls upon the development of new integrated circuits featuring increased energy efficiency while providing higher computation capabilities, i.e. better performance. The biomedical application of ECG analysis is an ideal target for an application-specific SoC implementation. However, new 12-lead ECG analyses algorithms are needed to meet the aforementioned goals. In this thesis, we present two novel algorithms for ECG analysis, namely the Autocorrelation-Function (ACF) based algorithm and the Fast Fourier Transform (FFT) based algorithm. In this respect, we explore the design space by analyzing different hardware and software architectures. As a result, we realize a design with twelve processors that can compute 3.5 million arithmetic computations and respect the real time hard deadline for our biomedical application (3.5-4 seconds), and that can deploy the ACF-based and FFT-based algorithms. Then, we investigate the configuration space looking for the most effective solution, performance and energy-wise. Consequently, we present three interconnect architectures (Single Bus, Full Crossbar, and Partial Crossbar) and compare them with existing solutions. The sampling frequencies of 2.2 KHz and 4 KHz, with 12 DSPs, are found to be the critical points for our Shared-Bus design and Crossbar architecture, respectively. We also show how our performance analysis methods can be applied to such a field of SoC design and with a specific purpose application in order to converge to a solution that is acceptable from a performance viewpoint, meets the real-time demands, and can be implemented with the present technologies while at the same time paving the way for easier and faster development. In order to connect our MPSoC solution to communication networks to transmit the medical results to a healthcare center, we come up with new protocols that will allow the integration of multiple networks on chips in a communication network. Finally, we present a methodology for HW/SW Codesign for application-specific systems (with focus on biomedical applications) that require a large number of computations since this will foster the convergence to solutions that are acceptable from a performance point of view.

iii

#### ACKNOWLEDGMENTS

"He who does not seek advice is a fool. His folly blinds him to Truth and makes him evil, stubborn and a danger to his fellow man."

Joubran Khalil Joubran- known also as Kahlil Gibran (1883 – 1931 A.D.)

Firstly, I would like to thank my advisor, Professor Axel Jantsch, whom I would simply describe as one of the greatest advisors I have ever seen for his knowledge, understanding, logic, and ease of cooperation. I thank Professor Axel from the bottom of my heart, for without him, surely and truly this thesis would not have existed.

I thank Dr. Robert Ronngren for his help and support all the time. Also many thanks are to Prof. Slimane Ben Slimane for the fruitful help and the nice talks. Special thanks are to Professor Luca Benini, whom I enjoy working with and learning from. In addition, I thank my friend professor Davide Bertozzi for creating a wonderful atmosphere at work. I have learned a lot from him, so I thank him for that! I thank Francesco Poletti for the great working days we spent in Italy. Infinite thanks are not enough for the great rose and wonderful person who never left me at any second of my hard and good times, Ms. Marilet De Andrade Jardin. Thank you very much for all the support, and I think that even if I give you everything I could, that won't be enough to really thank you for the amount of love, support and sweetness you showed. Special Thanks to my great friends Lennart Johansson, Victor Kordas, and Anders Nilsson, without whom I could not finish this thesis. Their understanding was very important! Many thanks go to Mr. Peter Ekman, Mr. Kaj Mikkos, and Ms. Paola Diaz whose support from ALMI for my patents was so great and unforgettable! Thank you very much! Thanks to Dr. Luc Onana Alima and his family for all the good times and the support. I also thank my friend Miguel Simon for the great work times and the wonderful laughs! Also I thank my friend Moustafa Chenine for the support and the good chats and advice. I also thank my friend Wim Michielsen for his advice and for being always supportive. I also thank all my friends, whose support was essential to finish this thesis. Special thanks to Katherine Stuart, whose love and support especially in my first few years in Sweden were basic for my success in many things including this thesis. I thank my brother Bassam Kayal for words can not describe how I trust him and count on him in most of my work and life issues especially in Sweden. I thank Bassam and his brothers and sisters, and mainly Mehdi and Adnan for the wonderful, fruitful and supportive chats and meetings! I also thank Zaidoon Jabbar, who was available to help me all the time! Moreover, I thank Mr. Khaled Khalil and his wonderful family. Khaled was very helpful and even just talking to him and getting his support saved me from wasting much of my time. Thank you very much Khaled to you and your understanding family! Many thanks are for Mohammad Saleh, who has helped me in many of my work issues in research and in many life matters. I will never forget the hard times that we went through together and also the nice good laughs. I thank my brother Nicolas Baron so much since, honestly, his presence in the hardest times of my life was the reason why I survived well. Many thanks fly to my brother Xavier Jombart and his beautiful lady Therese. I also thank my brother Giuseppe Russo for all his support and understanding. Special thanks to his family, his father Franco, his mother Franca, and his brother and all his uncles and aunts. With them, I always feel that I am with my family! Special thanks to the wonderful Calabria and Calabrians! Giuseppe remains in a very special place in my heart always! I thank also Dr. Carlo Spellucci, the traveling brother, iv

and all his family. Many thanks for the great help many times. I thank Dr. Fabio Curti for all the help and for being an excellent brother and friend. Thanks to Prof. Maurizio Di Ruscio and Prof. Carlo Uliveiri, who are excellent friends and researchers! Discussions with them led to endless ideas for me! Thanks to Francesco as well! Thanks to my brother Diego for his emails in science and in social affairs. Many thanks to my brother Nunzio Giovinazzi for his great support and wonderful laughs and time spent together! I also thank my friend Oscar Alcamo for the wonderful time we spent together! I thank Christine Ardini for the wonderful chats we had while in the lab in Italy. Special thanks to Cristina Severi, Samanta, and Giulia for the great wonderful times and laughs we had together! Thanks to my brother Biagio Ancarola and all his family. His mother is like my mother, his sisters are like my sister, and his father is like my father! I love them and miss them always, and I send love to all Napoli and all Italy! I also thank my brother Paolo Ponnzio for the great help and the great support for, really, without Paolo many things in my life would not have existed. Thanks Paolo. I also thank my brother and roommate Paolo Bonfiglio, without whom I would not have finished this thesis! Special thanks to my Italian brother Alessandro Baldoni and his support when needed. Many thanks go to my brother Gianluigi Baldessi for his great support and help when needed. Italy has a special place in my heart, the same way as Lebanon has exactly. Many thanks to Tamer ElNadi, who has helped me many times, and his support was always great! Thanks to Professor Mohammad Ismail for the great advice and the great times talking and laughing! Special thanks also to my friend George in Greece and to my friends Yannis and Kharis in Crete! Special thanks to my great friends, Mohamed Bechara, Hasan Khalifeh, and Mazen Hajjar, who never hesitated to help at any time. I remain grateful to them all. I also thank my wonderful and great hearted friend Jad Nasreddine for all the wonderful conversations and advice. I also thank my friend Jad Atallah for his endless support and for always being there whenever I needed him, and I really mean it, whenever I needed him. Moreover, thanks to Sleiman Bou Sleiman for he was always there, and thanks for all the help and support Sleex! Thanks to my long-time roommate and friend Dr. Tarvo Raudvere for all the good chats, advice and fruitful discussions. Thanks for Abbe Issa and Jonny Youssef for the great times, the times of serious work, the support, and the great advice! Thanks to Abu Khaled, Samer for the nice laughs and the Kabab! Special Thanks of course are to my brother Adel El Hassan for the great support, endless advice, and the indescribable help he always gave me! Thank you so much Adel to you and your family, and special thanks to your lady for the Mouloukhiya! Thanks to my friend Ibrahim Himad for his help all the time and for the support and the Mouloukhiya. I thank Mohammad Ali for the help with the tickets.

Very Special thanks go to Mrs. Christian Gizrawi, the councilor of the Lebanese embassy in Sweden. for her endless support and help. Thank you very much Christian, you will always remain a friend! Many thanks to my friend Sharbil Nader for the endless support he showed!

Special thanks to Ahmad Doughan who was always there ready to laugh throughout our friendship. Special thanks to my brother Ossama Dimassi for his help, support, and advice. Your presence by the phone and when I needed you was always important for my success. Thanks also to my friend Rajab for all his wonderful laughs, jokes, and the nice advice! Many thanks to my great brother Hisham Ghawgi for his wonderful support in Sweden! Many thanks fly to my friend Irene Kordahi for the funny chats we have all the time! Thanks to my friend Jihad Wehbe for all the good times and support! Special thanks to Mr. Sarat Samanta in Sweden for the time spent chatting, the good advice, and the wisdom.

I remain grateful to my family, in the USA, who never hesitated to help me. In particular thanks to the Great Lady Sue! Thank you very much for being a great mother! Thanks to the genius Dave Peterson, who

v

is not only family to be proud of, but also a very smart man, who solved many problems for me in life and scientifically! The endless love and support of Dave and Sue has been a great enrichment for my soul and life! I remain grateful to my mother and father in Lebanon, the Al Khatibs! Their endless love and support was the reason that made me what I am. Special thanks to my friend Richard Vine, who has been always supportive. Many thanks remain to my friend Dr. Loai Jalloul for his great help and support, as without him life would not have been the same! In the end, "What's Kebob" Loai? Many thanks to my friend Dr. Walid Ali Ahmad for all the great times we spent together laughing and joking. Thanks to Guy Davis and to Joseph. Guy's support was beyond description. His caring about my well being in many times is something I can not forget! I also thank Joseph for always being there! I would finally love to thank my "bestestest" friend Mr. Dudey Wudey III, Ian Marsh, soon Doctor Marsh for all the great times, laughs, and support! Deep thanks go to my uncle, Ph.D. and M.D. Ali Al Horr, who helped me understand all medical issues needed for this thesis. Many thanks and hugs to my great brother Wahid Al Kaisi, without whom I could not have done many things in this thesis! I miss you Wahid! "Lakaaan?" Many thanks to my friend Ahmad Abdallah at the AUB for his support on helping me understand ECG signals and their abnormalities. I also thank my great friend Anas Idris for all his support and the time spent together. I thank Amer Bzeih for all the wonderful times and support. Great thanks to Mr. Abu Antar, Hassan Zreik, who remains in a very special place in my heart for his support in logical thinking, in real friends' emotional support and advice, and in the discussions about the Dalai Lama.

Special thanks to the administrators in the ECS department, KTH, Hans, Julio, Richard, Enrico, Peter, Fredrik, and all others! Thanks to Carl Gustav Jansson for all the support and help! I thank Hans-Jörgen Rasmussen, Rita Fjällendahl, Angeta Herling, Lena Beronius, Rose-Marie Lövenstig, Gunnar Johansson, and Hans Larsson. I also thank Dr. Vlad Vlassov for all the nice chats and good advice.

Finally, and again I remain grateful to my families, in the USA and in the Lebanon, who never hesitated to help me. I also thank my brother Bassel Al Khatib for all his endless support. I thank my sister Raniem for the great conversations, emotional support, and love.

For all those who helped and I may have forgotten to mention, please forgive me and I thank you in this sentence.

vi

"The true wealth of a nation lies not in its gold or silver but in its learning, wisdom and in the uprightness of its sons."

Joubran Khalil Joubran- known as Kahlil Gibran

(1883 – 1931 A.D.)

vii

I dedicate this

To my families in the Lebanon and the USA

viii

## CONTENTS

| ABSTRACT    | II                                           | I |

|-------------|----------------------------------------------|---|

| ACKNOWL     | EDGMENTSIV                                   | 7 |

| CONTENTS    |                                              | ζ |

| LIST OF FIC | GURESXI                                      | I |

| LIST OF TA  | BLESXV                                       | I |

| ABBREVIA    | TIONSXVI                                     | I |

| NOMENCLA    | ATURESXXII                                   | I |

| CHAPTER 1   | INTRODUCTION                                 | 1 |

| 1.1.        | MOTIVATION                                   | 1 |

| 1.2.        | CONTRIBUTION                                 | 0 |

| 1.3.        | ORGANIZATION OF THE THESIS                   | 4 |

| CHAPTER 2   | BACKGROUND1                                  | 5 |

| 2.1.        | BIOMEDICAL APPLICATION BACKGROUND            | 5 |

| 2.1.1.      | The Twelve Lead ECG                          | 5 |

| 2.1.2.      | Current Steps in ECG Recording and Analysis  | 9 |

| 2.2.        | PREVIOUS WORK                                | 1 |

| 2.2.1.      | Software Algorithms                          | 1 |

| 2.2.1.1     | Algorithms for Ambulatory Patient Monitoring | 2 |

| 2.2.1.2     | Pan Tompkins                                 | 3 |

| 2.2.2.      | Hardware Systems                             | 5 |

| 2.3.        | SENSING AND FILTERING                        | 0 |

| 2.4.        | SOC AND MPSOC BACKGROUND                     | 1 |

| 2.5.        | METHODOLOGY                                  | 6 |

| CHAPTER 3   | NOVEL ECG ALGORITHMS FOR HW/SW CODESIGN      | 9 |

ix

Page

| 3.1.    | INTRODUCTION                                                   | 39  |

|---------|----------------------------------------------------------------|-----|

| 3.2.    | FILTERING AS A PRE-ANALYSIS NEED                               | 44  |

| 3.3.    | ECG ANALYSIS USING THE ACF-BASED ALGORITHM                     | 48  |

| 3.4.    | ECG ANALYSIS USING THE FFT-BASED ALGORITHM                     | 63  |

| 3.5.    | ECG ANALYSES-ALGORITHMS COMPARISON                             | 66  |

| 3.5.1.  | Comparison between Pan-Tompkins and the ACF Methods            | 66  |

| 3.5.1.  | 1. First Case for the Pan-Tompkins Algorithm Failure           | 66  |

| 3.5.1.  | 2. Second Case for Pan-Tompkins Algorithm Failure              | 67  |

| 3.5.2.  | Comparison between the ACF-Based and the FFT-Based Algorithms. | 68  |

| CHAPTER | 4 INTER-MULTICORE-CHIP COMMUNICATIONS                          | 71  |

| 4.1.    | PROTOCOLS FOR FITTING THE MPSOC SOLUTION IN THE BIG            |     |

|         | PICTURE SOLUTION                                               | 71  |

| 4.2.    | INTER-NOC COMMUNICATIONS                                       | 75  |

| 4.2.1.  | ENoP Principles                                                | 76  |

| 4.2.2.  | Algorithms                                                     | 77  |

| 4.3.    | THE SIMULATION ENVIRONMENT                                     | 79  |

| 4.4.    | SUMMARY                                                        | 82  |

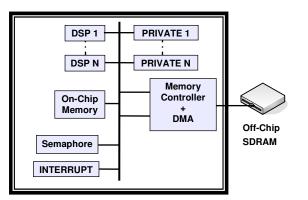

| CHAPTER | 5 MPSOC HARDWARE-SOFTWARE CODESIGN                             | 83  |

| 5.1.    | INTRODUCTION                                                   | 83  |

| 5.2.    | Processor Cores                                                | 85  |

| 5.3.    | SW FLOATING POINT VS. FIXED POINT CODE                         | 86  |

| 5.4.    | COMPARISON BETWEEN COMPUTATIONAL CORES                         | 87  |

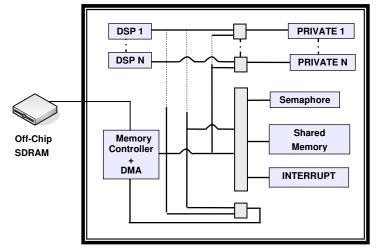

| 5.5.    | EXPERIMENTAL ENVIRONMENT AND MPSOC ARCHITECTURE                | 88  |

| 5.6.    | REQUIRED LEVEL OF HW PARALLELISM                               | 91  |

| 5.6.1.  | Experiments Description                                        | 92  |

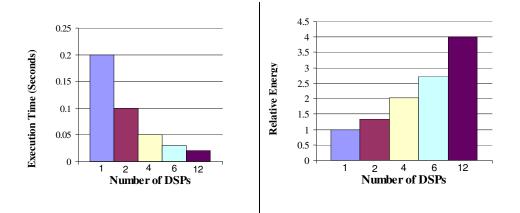

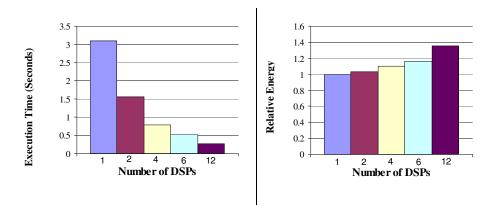

| 5.6.2.  | Experimental Results                                           | 92  |

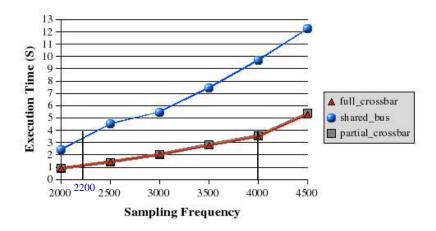

| 5.6.3.  | Scalability                                                    | 94  |

| 5.7.    | SOLUTIONS COMPARISON                                           | 97  |

| 5.8.    | SUMMARY                                                        | 102 |

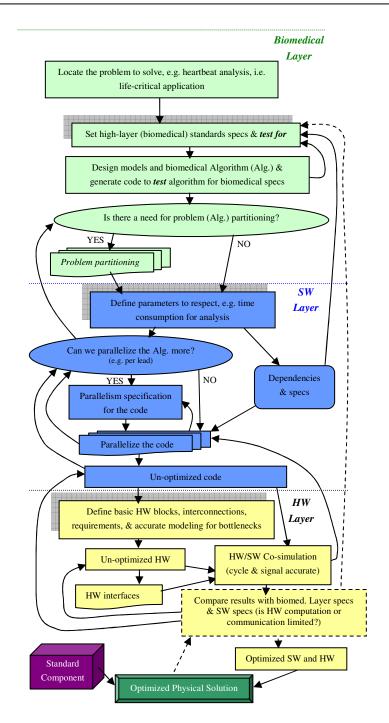

| CHAPTER | 6 THE RESULTING METHODOLOGY                                    | 105 |

| 6.1.    | INTRODUCTION                                                   | 105 |

| 6.2.    | VIRTUAL PLATFORM                                               | 106 |

| 6.3.    | LIFE-CRITICAL APPLICATION                                      | 106 |

| 6.4.    | HIGH TASK LEVEL PARALLELISM                                    | 106 |

| 6.5.    | COMMUNICATION BANDWIDTH REQUIREMENTS                           | 107 |

|         |                                                                |     |

х

| 6.6.   | COMPUTATION AND COMMUNICATION PARALLELISM              | 107 |

|--------|--------------------------------------------------------|-----|

| 6.7.   | EXAMPLE OF A RESULTING HW AND SW ARCHITECTURE          | 111 |

| 6.8.   | METHODOLOGY IN BRIEF AND TRADEOFFS                     |     |

| 6.9.   | SUMMARY                                                | 113 |

| СНАРТЕ | R 7 CONCLUSIONS                                        | 115 |

| 7.1.   | CONCLUDING REMARKS                                     | 115 |

| 7.2.   | SUMMARY                                                | 119 |

| СНАРТЕ | R 8 OPEN ISSUES & FUTURE WORK                          |     |

| REFERE | NCES                                                   | 125 |

| APPEND | ICES                                                   | 149 |

| Appeni | DIX 1 AUTOCORRELATION FUNCTION AND ITS PROPERTIES      | 149 |

| APPENI | DIX 2 DETAILED DESCRIPTION OF THE FFT-BASED ALGORITHM. |     |

| Appeni | DIX 3 WAVELET OVERVIEW                                 | 156 |

| APPENI | DIX 4 THE DEFINITION OF "METHODOLOGY"                  |     |

xi

## LIST OF FIGURES

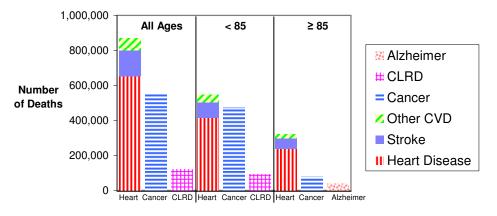

| FIGURE 1. NUMBER OF DEATHS FOR THE FOUR LARGEST CAUSES OF DEATHS: HEART     |

|-----------------------------------------------------------------------------|

| DISEASES (CVD AND STROKE), CANCER, CHRONIC LOWER RESPIRATORY                |

| DISEASE (CLRD), AND ALZHEIMER; FROM THE HEART DISEASE AND STROKE            |

| STATISTICS-2008 UPDATE [69]. THE NUMBERS ON TOP ARE IN YEARS OF AGE:        |

| THE FIRST PART ON THE LEFT SIDE INCLUDES PATIENTS FROM ALL AGES. THE        |

| MIDDLE PART CONTAINS THE STATISTICS FOR PATIENTS UNDER 85 YEARS OLD.        |

| The part on the right includes the statistics for the patients above $85$   |

| YEARS OLD                                                                   |

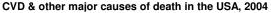

| FIGURE 2. ESTIMATED DIRECT AND INDIRECT COSTS (TOTAL OF USD 326.1 BILLION)  |

| OF MAJOR CVD DISEASES AND STROKE IN THE USA IN 2008; FROM THE HEART         |

| DISEASE AND STROKE STATISTICS-2008 UPDATE [69]4                             |

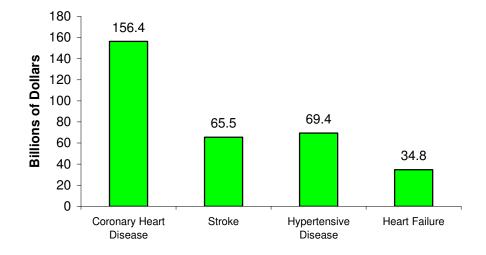

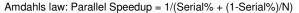

| FIGURE 3. HEALTHCARE SOLUTION SCENARIO FOR AID AT THE DISASTER POINT (POINT |

| OF NEED). A SCENARIO WHERE THE SMALL SIZE, SMALL WEIGHT, AND HIGH           |

| COMPUTATIONAL ABILITY OF MPSOC PROVIDE A POTENTIAL FOR APPLICABLE           |

| SW SOLUTIONS FOR HEALTHCARE IMPLEMENTED ON AN MPSOC, E.G. HEART             |

| ANALYSIS AT THE DISASTER SITE USING MPSOCS THAT ARE CONNECTED VIA A         |

| COMMUNICATION LINK TO A HEALTHCARE CENTER. THE CONNECTION CAN BE            |

| VIA A SATELLITE NETWORK OR OTHER COMMUNICATIONS NETWORK. SATELLITE          |

| AID REMAINS INTACT AND COVERS LARGE AREAS WHEN GROUND DISASTERS             |

| OCCUR                                                                       |

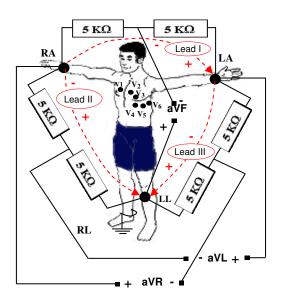

| FIGURE 4. INTERCONNECTIONS OF THE 12-LEAD ECG TECHNIQUE; RA, LA, LL, & RL   |

| (G) are the right arm, left arm, left leg, and right leg sensors. RL is     |

| GROUNDED (G). THE AUGMENTED LEADS ARE AVR, AVF, AND AVL. THE CHEST          |

| LEADS ARE V1, V2, V3, V4, V5, AND V6                                        |

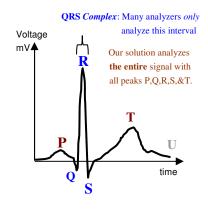

| FIGURE 5. A TYPICAL ECG SIGNAL; LEAD I FOR A NORMAL HEART                   |

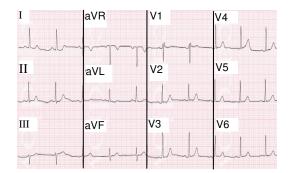

| FIGURE 6. COMPLETE PAPER READOUT OF THE 12-LEAD ECG, WHICH IS NOT           |

| ACCURATE TO SEE PEAKS NOR EASY TO READ FOR LONG RECORDINGS                  |

| FIGURE 7. ZOOM IN LEAD I FROM THE PAPER PRINTOUT OF THE 12-LEAD ECG SIGNALS |

| OF FIGURE 6. THIS ZOOMING SHOWS HOW READING THE SIGNAL IS DEPENDENT         |

| ON THE PHYSICIAN'S EYES, HENCE MAKES ANALYSIS MORE DIFFICULT                |

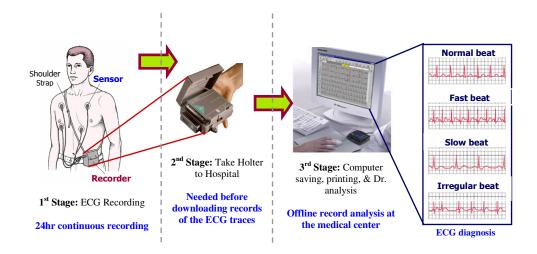

| FIGURE 8. CURRENT METHODS TO RECORD ECG DATA FOR LONG NUMBER OF HOURS       |

| AND THEN CARRYING THE RECORDED DATA TO THE HEALTHCARE CENTER FOR            |

| PRINTING AND ANALYSIS                                                       |

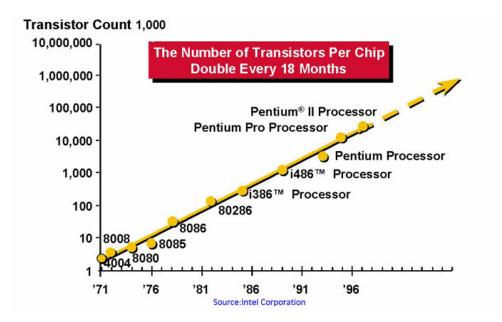

| FIGURE 9. NUMBER OF TRANSISTORS ON CHIP DOUBLE EVERY 18 MONTHS              |

| xii                                                                         |

Page

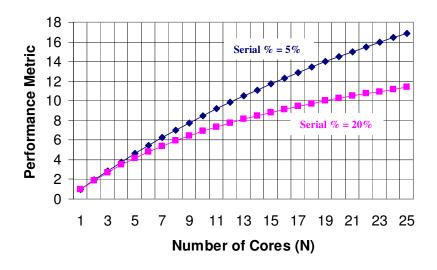

| FIGURE 10. AN APPROXIMATION OF THE PERFORMANCE SCALING VS. NUMBER OF                         |

|----------------------------------------------------------------------------------------------|

| CORES ON A CHIP. HENCE PARALLELIZING SW IS A KEY POINT FOR THE SUCCESS                       |

| OF MULTICORE SYSTEMS SINCE PERFORMANCE IS A KEY ISSUE FOR SUCCESS                            |

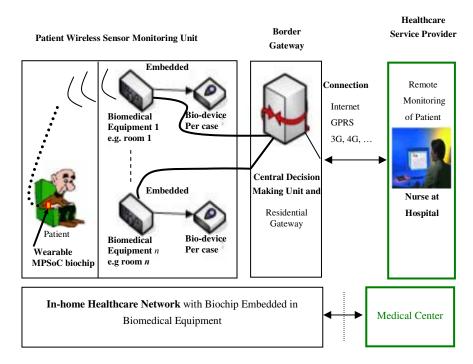

| FIGURE 11. BIOCHIP DEPLOYMENT OVER A HEALTHCARE NETWORK FOR PATIENT                          |

| MONITORING AND REAL-TIME ANALYSIS AT THE POINT OF NEED                                       |

| FIGURE 12. HOME HEALTHCARE SCENARIO WHERE BIOMEDICAL APPLICATIONS ON A                       |

| WEARABLE MPSOC CAN BE APPLIED. FOR INSTANCE, THE PATIENT CAN HAVE HIS                        |

| HEARTED MONITORED, VIA AN APPLICATION SPECIFIC MPSoC42                                       |

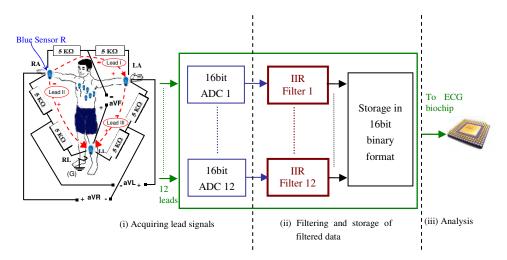

| FIGURE 13. THE SYSTEM FOR SENSING AND FILTERING OF ECG LEAD SIGNALS BEFORE                   |

| SENDING DATA TO THE ECG BIOCHIP FOR ANALYSIS. BLUE SENSOR R IS FROM                          |

| AMBU INC. [15]                                                                               |

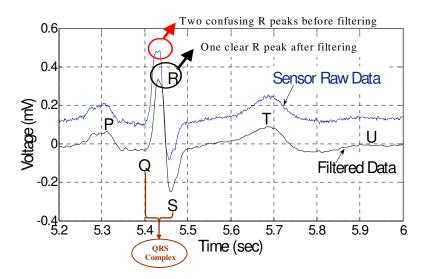

| FIGURE 14. ECG RAW AND FILTERED DATA (LEAD I)                                                |

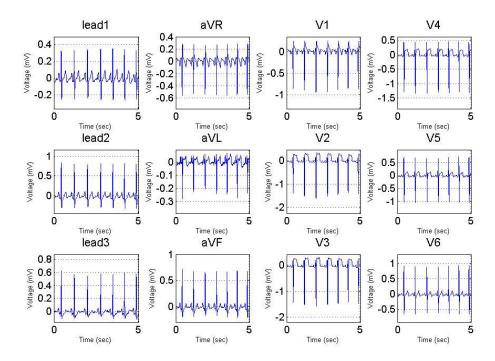

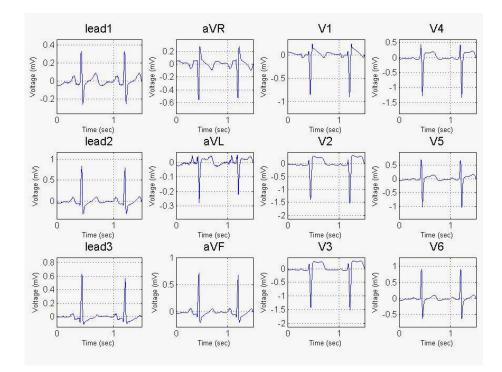

| FIGURE 15. TWELVE FILTERED ECG LEADS. COMPARING WITH FIGURE 6 OF THE                         |

| COMPLETE PAPER READOUT WE CAN SEE THE DIFFERENCE IN THE ABILITY TO                           |

| DIGITALLY PROCESS DATA WITH HIGHER QUALITY                                                   |

| FIGURE 16. TWELVE FILTERED ECG LEADS. COMPARING WITH FIGURE 15, WE CAN                       |

| DIGITALLY ZOOM INTO THE HEART CYCLES WE NEED. COMPARING WITH FIGURE                          |

| 6 OF THE COMPLETE PAPER READOUT WE CAN SEE THE DIFFERENCE IN THE                             |

| ABILITY TO DIGITALLY PROCESS DATA WITH HIGHER QUALITY                                        |

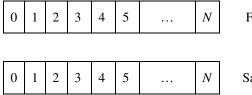

| FIGURE 17. THE FIRST STEP IN CALCULATING THE ACF. THE NUMBERS FROM 0 TO $N$                  |

| REPRESENT THE VALUE OF THE INDEX N                                                           |

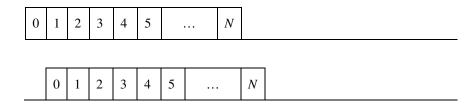

| FIGURE 18. THE SECOND STEP IN THE CALCULATION OF THE ACF. THE NUMBERS                        |

| FROM 0 TO N REPRESENT THE VALUE OF THE INDEX N                                               |

| Figure 19. The N <sup>th</sup> step in calculating the ACF. The numbers from 0 to N          |

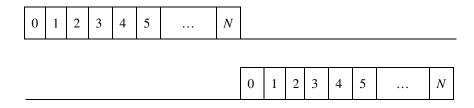

| REPRESENT THE VALUE OF THE INDEX N                                                           |

| Figure 20. The first step in calculating the ACF for periodic $Y(T)$ . The                   |

| NUMBERS FROM 0 TO $N$ represent the value of the index $n$ This is used                      |

| FOR THE CALCULATION OF $R_{\rm Y}[0]$                                                        |

| Figure 21. The second step in calculating the ACF for periodic $y(t)$ . The                  |

| NUMBERS FROM 0 TO N REPRESENT THE VALUE OF THE INDEX N. THIS IS USED                         |

| FOR THE CALCULATION OF $R_{\rm y}[1]$                                                        |

| Figure 22. The third step in calculating the ACF for periodic $y(T)$ . The                   |

| NUMBERS FROM 0 TO N REPRESENT THE VALUE OF THE INDEX N. THIS IS USED                         |

| FOR THE CALCULATION OF $R_{\rm y}[2]$                                                        |

| FIGURE 23. THE $4^{\text{TH}}$ step in calculating the ACF for periodic $Y(T)$ . Here we can |

| SEE THE CLEAR OVERLAP AGAIN OF IDENTICAL ELEMENTS OF THE SERIES. THIS IS                     |

| USED FOR THE CALCULATION OF $R_{\rm Y}[3]$                                                   |

xiii

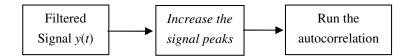

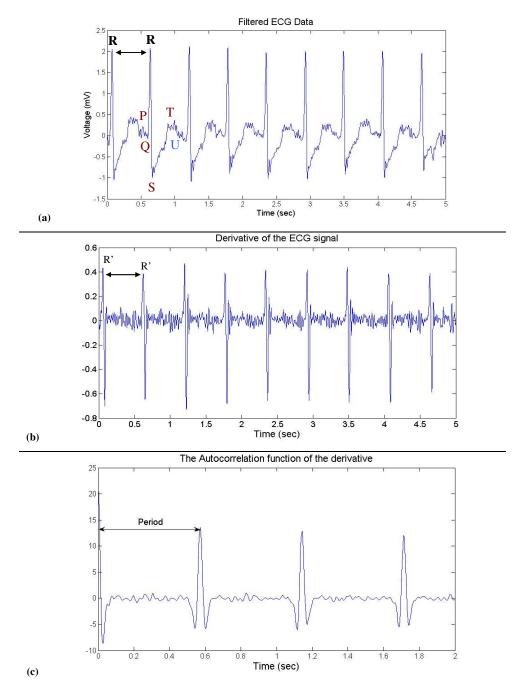

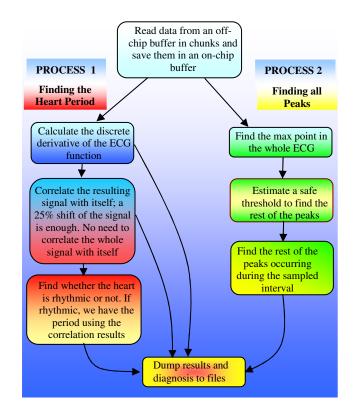

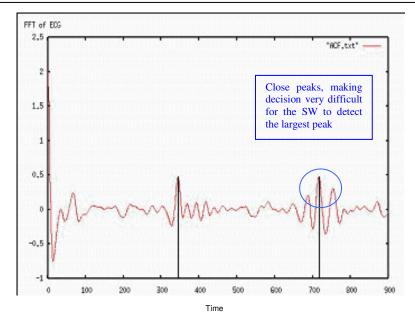

| FIGURE 24. ILLUSTRATION OF THE STEP BETWEEN THE FILTERED SIGNAL AND ITS ACF58<br>FIGURE 25. HEART PERIOD ANALYSIS: (A) ECG SIGNAL PEAKS P, Q, R, S, T, AND U;<br>(B) DERIVATIVE AMPLIFYING R PEAKS; (C) AUTOCORRELATION OF THE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DERIVATIVE CHARACTERIZED BY SIGNIFICANT PERIODIC PEAKS HAVING THE SAME VALUE AS THE PERIOD OF THE ECG SIGNAL IN (B) AND THUS (A)                                                                                               |

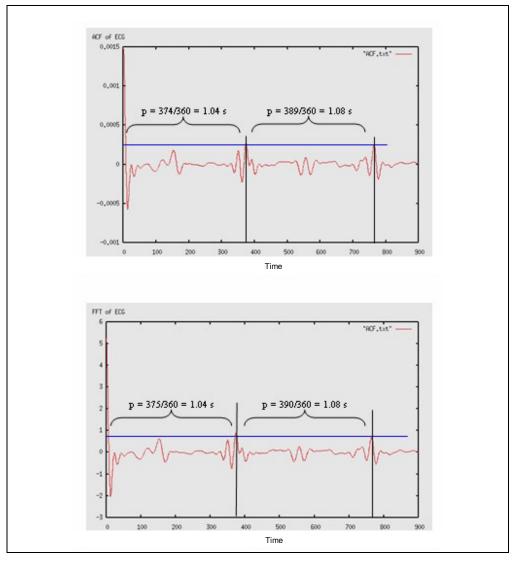

| FIGURE 26. THE AUTOCORRELATION FUNCTION-BASED METHOD FOR ECG ANALYSIS63                                                                                                                                                        |

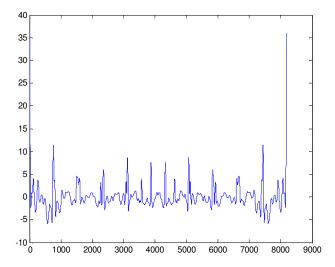

| FIGURE 27. AUTOCORRELATION DATA FROM THE FFT-BASED ALGORITHM. TO GET                                                                                                                                                           |

| THE HEART PERIOD FROM THIS DATA, WE TAKE THE PEAK AT THE ORIGIN AND THE                                                                                                                                                        |

| NEXT PEAK AND THEN SUBTRACT THE INDICES AND DIVIDE BY THE SAMPLING                                                                                                                                                             |

| FREQUENCY65                                                                                                                                                                                                                    |

| FIGURE 28. PERIOD DETECTION USING FFT-BASED ALGORITHM TO CALCULATE THE                                                                                                                                                         |

| AUTOCORRELATION COEFFICIENTS                                                                                                                                                                                                   |

| FIGURE 29. PERIOD DETECTION USING THE ACF-BASED DIRECT METHOD TO                                                                                                                                                               |

| CALCULATE THE AUTOCORRELATION COEFFICIENTS FOR THE SAME PATIENT                                                                                                                                                                |

| DATA PRESENTED IN FIGURE 28                                                                                                                                                                                                    |

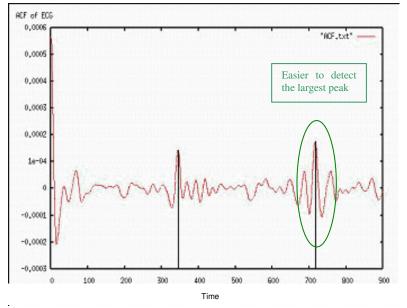

| FIGURE 30. NUMBER OF MULTIPLICATIONS FOR THE DIRECT ACF-BASED METHOD AND                                                                                                                                                       |

| THE FFT-BASED METHOD FOR OUR BIOMEDICAL ALGORITHM                                                                                                                                                                              |

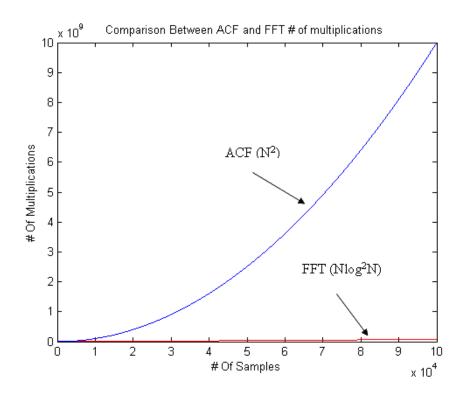

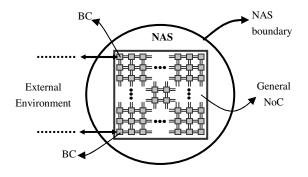

| FIGURE 31. NOC AS AN AUTONOMOUS SYSTEM (NAS). A BASIC BLOCK FOR INTER-                                                                                                                                                         |

| NOC COMMUNICATIONS. BCS RUN THE ENOP ON THE EXTERNAL NOC LINK AND                                                                                                                                                              |

| INOP ON THE INTERNAL LINK                                                                                                                                                                                                      |

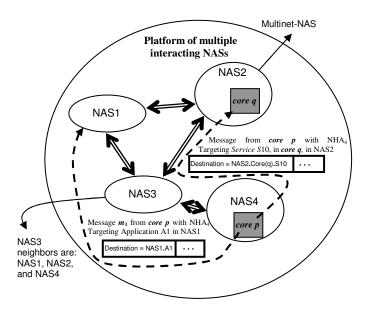

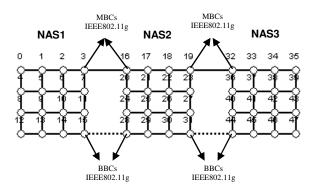

| FIGURE 32. LOGICAL TOPOLOGY OF MULTIPLE NASS OF PHYSICALLY CONNECTED                                                                                                                                                           |

| NoCs (or BIONOCS IN EMERGENCY SITUATION FOR 4 PATIENTS) THAT ARE                                                                                                                                                               |

| LOGICALLY INTERACTING TO PROVIDE A LARGER PLATFORM WITH HIGHER                                                                                                                                                                 |

| CAPACITY AND MORE CAPABILITIES IN ORDER TO SERVE SOME COMMON                                                                                                                                                                   |

| APPLICATION OR PURPOSE [73]                                                                                                                                                                                                    |

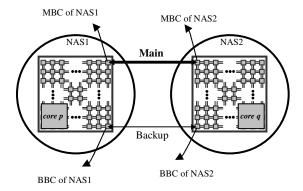

| FIGURE 33. TWO NASS INTERCONNECTED USING VIA A MAIN LINK AND A BACKUP                                                                                                                                                          |

| LINK. THE CHOICE OF WHICH CONNECTION WILL BE THE MAIN AND WHICH WILL                                                                                                                                                           |

| BE THE BACKUP IS MADE BY THE ENOP. MAIN AND BACKUP CONNECTIONS MAY                                                                                                                                                             |

| BE WIRED OR WIRELESS. IN WIRELESS INTER-NOC COMMUNICATIONS, EACH OF                                                                                                                                                            |

| THE MAIN AND BACKUP USES A DIFFERENT FREQUENCY CHANNEL TO AVOID                                                                                                                                                                |

| COLLISION                                                                                                                                                                                                                      |

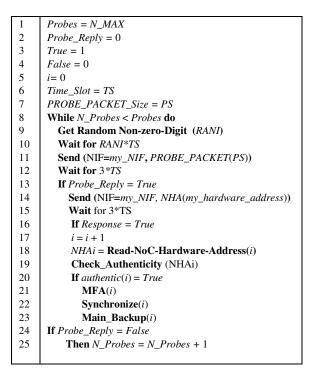

| FIGURE 34. NND ALGORITHM DISCOVERING AND AUTHENTICATING A NEIGHBORING                                                                                                                                                          |

| NAS THEN DECIDING THE MESSAGE FORMAT, SYNCHRONIZING AND CHOOSING                                                                                                                                                               |

| WHICH LINK IS MAIN AND WHICH IS BACKUP [79]                                                                                                                                                                                    |

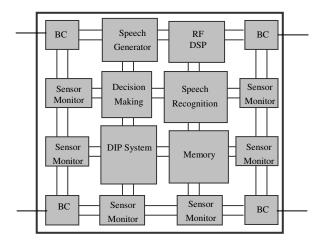

| FIGURE 35. BIONOC DESIGN FOR THE EMERGENCY CASE MONITORING EXAMPLE                                                                                                                                                             |

| FIGURE 36. WNOCS SIMULATION ENVIRONMENT. EACH NAS CORRESPONDS TO A                                                                                                                                                             |

| WNOC WITH 16 CORES AS DESCRIBED IN FIGURE 35. THE NUMBERS OVER THE                                                                                                                                                             |

xiv

| NODES REVEAL THE HARDWARE ADDRESS OF EACH CORE OF THE 16 CORES OF         |

|---------------------------------------------------------------------------|

| THE BIONOC SHOWN IN FIGURE 35. THE MBCS AND THE BBCS RUN                  |

| IEEE802.11G AT 54MBPS80                                                   |

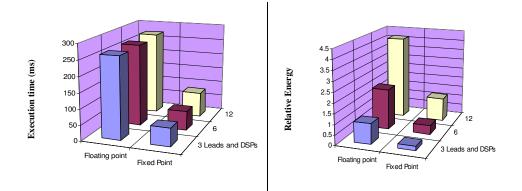

| FIGURE 37. COMPARISON BETWEEN DIFFERENT CODE IMPLEMENTATIONS FOR THE      |

| ANALYSIS OF THE 3-LEAD, 6-LEAD AND 12-LEAD ECG. DATA ANALYSIS FOR         |

| EACH LEAD IS COMPUTED ON A SEPARATE PROCESSOR CORE. SAMPLING              |

| FREQUENCY OF INPUT DATA WAS 250HZ. SYSTEM OPERATING FREQUENCY WAS         |

| 200 MHz                                                                   |

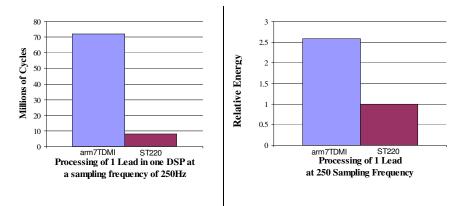

| FIGURE 38. COMPARING ARM7TDMI WITH ST200 DSP PERFORMANCES, WHEN           |

| PROCESSING 1 LEAD AT 250Hz SAMPLING FREQUENCY                             |

| FIGURE 39. SINGLE BUS ARCHITECTURE WITH STBUS INTERCONNECT                |

| FIGURE 40. CROSSBAR ARCHITECTURE WITH STBUS INTERCONNECT                  |

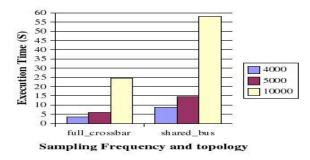

| FIGURE 41. EXECUTION TIME AND RELATIVE ENERGY OF SHARED BUS AT 250Hz      |

| SAMPLING FREQUENCY                                                        |

| FIGURE 42. EXECUTION TIME AND RELATIVE ENERGY OF SHARED BUS AT 1000Hz     |

| SAMPLING FREQUENCY                                                        |

| FIGURE 43. CRITICAL SAMPLING FREQUENCIES FOR 3 ARCHITECTURES: (1) SHARED  |

| BUS, (2) FULL CROSSBAR, AND (3) PARTIAL CROSSBAR. THE 3.5SECONDS REAL-    |

| TIME LIMIT CAN BE RESPECTED AND ACHIEVED WITH 2200Hz SAMPLING             |

| FREQUENCY WHEN THE SHARED BUS ARCHITECTURE IS USED AND WITH 4000Hz        |

| sampling frequency when either the Full crossbar architecture or          |

| THE PARTIAL CROSSBAR ARCHITECTURE IS USED                                 |

| FIGURE 44. ANALYSIS-TIME INVESTIGATION WITH INCREASING FREQUENCIES (UP TO |

| 10 KHz) FOR THE ECG APPLICATION96                                         |

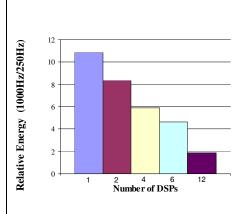

| FIGURE 45. RELATIVE ENERGY RATIOS BETWEEN THE 1000Hz and the 250Hz        |

| SAMPLING FREQUENCY EXPERIMENTS                                            |

| FIGURE 46. METHODOLOGY USED FOR HIGH-END BIOMEDICAL APPLICATION HW/SW     |

| CO-DESIGN (APPLIED FOR ECG ANALYSIS)                                      |

| FIGURE 47. COMPARISON BETWEEN THE ACF-BASED ALGORITHM AND THE FFT-        |

| BASED ALGORITHM                                                           |

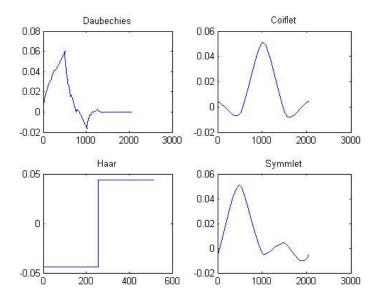

| FIGURE 48. EXAMPLE OF WAVELET FUNCTIONS158                                |

xv

## LIST OF TABLES

| TABLE 1. BIONOCSIM++ RESULTS FOR REAL SCENARIO OF A TWO BIONOC     |     |

|--------------------------------------------------------------------|-----|

| SENSOR NETWORK                                                     | 80  |

| TABLE 2. BIONOC SIMULATION RESULTS OXYGEN LEVEL SENSORS OF THE     |     |

| ENVIRONMENT SHOWN IN FIGURE 36                                     | 81  |

| TABLE 3. COMPARISON BETWEEN ECG ANALYSIS RESEARCH SOC SOLUTION     |     |

| [115], AVAILABLE SOC COMMERCIAL SOLUTION [59], AND OUR THREE       |     |

| MPSOC DESIGNS: ST-PCB IS PARTIAL CROSSBAR, ST-CB IS FULL           |     |

| CROSSBAR, AND ST-SB is the Shared Bus solution. $F_{\rm S}$ is the |     |

| SAMPLING FREQUENCY                                                 | 101 |

Page

xvi

## **ABBREVIATIONS**

| 3G     | Third Generations for Mobile Communications                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACF    | Autocorrelation Function                                                                                                                                                                |

| ADC    | Analog to Digital Converter                                                                                                                                                             |

| ARM    | Advanced RISC Machine, and prior to that Acorn RISC<br>Machine, is a computer processor architecture developed by<br>ARM Limited that is widely used in a number of embedded<br>designs |

| ASIC   | Application-Specific Integrated Circuit                                                                                                                                                 |

| aVF    | Augmented Lead F label in the ECG technique                                                                                                                                             |

| aVL    | Augmented Lead L label in the ECG technique                                                                                                                                             |

| aVR    | Augmented Lead R label in the ECG technique                                                                                                                                             |

| AWGN   | Additive White Gaussian Noise                                                                                                                                                           |

| BBC    | Backup Border Core                                                                                                                                                                      |

| BC     | Border Core in the NoC Autonomous System Proposed                                                                                                                                       |

| BIONoC | Biomedical Network-on-Chip                                                                                                                                                              |

| BLIF   | Berkeley Logic Interchange Format, to describe a logic-level hierarchical circuit in textual form                                                                                       |

| BPM    | Beat Per Minute                                                                                                                                                                         |

| CLRD   | Chronic Lower Respiratory Disease                                                                                                                                                       |

| CFSM   | Co-design Finite State Machine                                                                                                                                                          |

| CVD    | Cardiovascular Disease                                                                                                                                                                  |

| CPU    | Central Processing Unit                                                                                                                                                                 |

xvii

| DFT         | Discrete Fourier Transform                                                                                                                                                                                                                                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP         | Digital Image Processor                                                                                                                                                                                                                                                                                                     |

| DMA         | Dynamic Memory Allocation                                                                                                                                                                                                                                                                                                   |

| DSP         | Digital Signal Processing                                                                                                                                                                                                                                                                                                   |

| DVB         | Digital Video Broadcast, used in Satellite communications                                                                                                                                                                                                                                                                   |

| DVB-RCS     | DVB-Return Channel Satellite, a special technique for more reliability in DVB satellite communications                                                                                                                                                                                                                      |

| DVFS        | Dynamic Voltage and Frequency Scaling is a technique that<br>consists of varying the frequency and voltage of a<br>microprocessor in real-time according to processing needs. This<br>technique is used both for power-saving during off peak times,<br>and as a protective measure to avoid over-temperature<br>conditions |

| ECG         | Electrocardiogram, a set of heart signals (also known as EKG)                                                                                                                                                                                                                                                               |

| EKG         | Electrocardiogram, a set of heart signals (also known as ECG)                                                                                                                                                                                                                                                               |

| ENoP        | External NoC Protocol                                                                                                                                                                                                                                                                                                       |

| FFT         | Fast Fourier Transform                                                                                                                                                                                                                                                                                                      |

| FIR         | Finite Impulse Response                                                                                                                                                                                                                                                                                                     |

| FPGA        | Field-Programmable Gate Array                                                                                                                                                                                                                                                                                               |

| FSM         | Finite State Machine                                                                                                                                                                                                                                                                                                        |

| GNTS        | Global NAS Timing and Synchronization protocol                                                                                                                                                                                                                                                                              |

| GPRS        | General Packet Radio Service                                                                                                                                                                                                                                                                                                |

| HDL         | Hardware Description Language                                                                                                                                                                                                                                                                                               |

| HW          | Hardware                                                                                                                                                                                                                                                                                                                    |

| HRV         | Heart Rate Variability                                                                                                                                                                                                                                                                                                      |

| IC<br>xviii | Integrated Circuit                                                                                                                                                                                                                                                                                                          |

| ICT    | Information and Communication Technology                                                                                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IFFT   | Inverse Fast Fourier Transform (Inverse FFT)                                                                                                                                                                                                               |

| IIR    | Infinite Impulse Response; IIR Systems and filters have an<br>impulse response function, which is non-zero over an infinite<br>length of time. This is in contrast to finite impulse response<br>filters (FIR) which have fixed-duration impulse responses |

| ILP    | Instruction Level Parallelism                                                                                                                                                                                                                              |

| INoP   | Internal NoC Protocol                                                                                                                                                                                                                                      |

| IP     | Intellectual Property                                                                                                                                                                                                                                      |

| IT     | Information Technology                                                                                                                                                                                                                                     |

| LA     | Left Arm sensor label in the ECG technique                                                                                                                                                                                                                 |

| LL     | Left Leg sensor label in the ECG technique                                                                                                                                                                                                                 |

| MAC    | Medium Access Control                                                                                                                                                                                                                                      |

| MBC    | Main Border Core in the NAS model                                                                                                                                                                                                                          |

| MF     | Matched Filter                                                                                                                                                                                                                                             |

| MFA    | Message Format Agreement protocol in the NAS protocols                                                                                                                                                                                                     |

| MPSoC  | Multiprocessor System on Chip                                                                                                                                                                                                                              |

| NAS    | NoC as an Autonomous System                                                                                                                                                                                                                                |

| NIC    | Network Interface Card                                                                                                                                                                                                                                     |

| NND    | NAS Neighbor Discovery                                                                                                                                                                                                                                     |

| NoA    | Network-on-Chip Authentication                                                                                                                                                                                                                             |

| NoC    | Network on Chip                                                                                                                                                                                                                                            |

| PC     | Personal Computer                                                                                                                                                                                                                                          |

| PCMCIA | Personal Computer Memory Card International Association is<br>an international standards body that defines and promotes the                                                                                                                                |

xix

PC Card. PCMCIA now is used to mean a PC card

| PDA   | Personal Digital Assistant, is a handheld computer            |

|-------|---------------------------------------------------------------|

| QoS   | Quality of Service                                            |

| RA    | Right Arm sensor label in the ECG technique                   |

| RAM   | Random Access Memory                                          |

| RF    | Radio Frequency                                               |

| RISC  | Reduced Instruction Set Computer                              |

| RTEMS | Real-Time Executive Multiprocessor Systems                    |

| S/N   | Signal-to-Noise Ratio                                         |

| SCI   | Serial Communication Interface                                |

| SDRAM | Synchronous Dynamic Random Access Memory                      |

| SIS   | Silicon Integrated System                                     |

| SoC   | System on Chip                                                |

| SQRS  | Single-channel QRS detector, an ECG ambulatory algorithm      |

| STFT  | Short-Time Fourier Transform                                  |

| SW    | Software                                                      |

| UN    | United Nations                                                |

| USD   | United States Dollars                                         |

| VHSIC | Very High Speed Integrated Circuit                            |

| VLIW  | Very Long Instruction Word, refers to a CPU architecture that |

|       | uses instruction level parallelism (ILP)                      |

| WHO   | World Health Organization of the United Nations               |

|       |                                                               |

| WNoC  | Wireless NoC                                                  |

xх

| WQRS | Single-channel QRS detector based on length transform, an  |

|------|------------------------------------------------------------|

|      | ECG ambulatory algorithm                                   |

| WSN  | Wireless Sensor Network                                    |

| XNF  | Xilinx Netlist Format, a HDL for electronic circuit design |

|      | developed by Xilinx, Inc.                                  |

### **Software and Communication Abbreviations**

| C/C++   | C and C++ computer programming languages                                                      |

|---------|-----------------------------------------------------------------------------------------------|

| MATLAB  | MATLAB software and computer programming language                                             |

| MPARM   | Multiprocessor                                                                                |

| Satcom  | Satellite Communications                                                                      |

| SystemC | System C computer language                                                                    |

| Verilog | Verilog HDL is a hardware description language used to design and document electronic systems |

| VHDL    | VHSIC Hardware Description Language                                                           |

### Unit abbreviations

| μm  | micrometer; equals $10^{-6}$ meter                                                                |

|-----|---------------------------------------------------------------------------------------------------|

|     |                                                                                                   |

| μs  | micro seconds, equals 10 <sup>-6</sup> seconds                                                    |

| bit | A binary digit that can be of value either 0 or 1                                                 |

| bps | bits per second                                                                                   |

| В   | Byte: Information Unit equal to 8bits                                                             |

| G   | Giga; equals $10^9$ , but for bits and bytes (binary data storage) it is equivalent to $1K*1K*1K$ |

xxi

| GHz     | Giga Hertz                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------|

| Hz      | Hertz, unit of frequency                                                                                         |

| К       | Kilo, equals 10 <sup>3</sup> , but for bits and bytes (binary data storage) it 1Kbytes is equivalent to 1024bits |

| KHz     | Kilo Hertz                                                                                                       |

| М       | Mega, equals $10^6$ , but for bits and bytes (binary data storage) it<br>is equivalent to $1K*1K = 1024*1024$    |

| MB      | Mega Bytes                                                                                                       |

| MHz     | Mega Hertz                                                                                                       |

| mm      | millimeters, equals to 10 <sup>-3</sup> meters                                                                   |

| ms      | milliseconds, equals to $10^{-3}$ seconds                                                                        |

| mV      | mill-volts, equals to $10^{-3}$ volts                                                                            |

| P4      | Pentium Four                                                                                                     |

| s, secs | second(s)                                                                                                        |

#### Definitions

| Granularity  | Granularity is the relative scale or size, and it can be the relative<br>level of detail that characterizes an object or activity. It reveals<br>how much a system contains separate components called<br>granules. |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multinet-NAS | A NAS that is interconnected to more than one NAS at the same time.                                                                                                                                                 |

| Reliability  | Bit error rates, bit loss, packet loss; Note that these terms are<br>often mixed up, and the term QoS is sometimes used to refer to<br>what we would rather call service guarantees or quality in<br>general        |

xxii

## NOMENCLATURES

| $\frac{\partial y}{\partial t}$ (.) | Partial derivative of $y$ with respect to $t$                                                                                                   |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| а                                   | a is the vector that contains the filter coefficients for output y of<br>the IIR filter                                                         |

| $A(t), A[n], ACF_{y}(.)$            | Autocorrelation function of the signal y                                                                                                        |

| authentic(.)                        | Function in the NND of the ENoP to check if the communicati9ng NoC can be authenticated                                                         |

| b                                   | b is the vector that contains the filter coefficients for signal <i>x</i> , <i>the input signal for the IIR filter</i>                          |

| D(.)                                | Derivative                                                                                                                                      |

| DFT(.)                              | Discrete Fourier Transform                                                                                                                      |

| $f_s$                               | Sampling frequency                                                                                                                              |

| g(t)                                | The window function used to slice the signal and apply the Fourier Transform in the Wavelets                                                    |

| h                                   | Response function                                                                                                                               |

| H(z)                                | Transfer function of the filter                                                                                                                 |

| k                                   | index in the discrete signal function                                                                                                           |

| l                                   | index in the discrete function                                                                                                                  |

| L                                   | Number of Lags, i.e. needed number to have enough calculations to get the period of the signal                                                  |

| m                                   | Index used in equations                                                                                                                         |

| Main_Backup(.)                      | Function in the NND of the ENoP that determines which link is<br>the Main link and which is the Backup link between<br>neighboring NASs (NoCs). |

xxiii

| MFA(.)              | Function in the NND of the ENoP that determines the message<br>sizes and formats used for communication between two<br>neighboring NoCs |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| min(x, y)           | Minimum function that returns the minimum of $x$ or $y$                                                                                 |

| n                   | Index used in equations                                                                                                                 |

| Ν                   | The maximum index of $n$ , i.e. the total number of samples is $N+1$                                                                    |

| N_MAX               | The Maximum number used in the ENoP algorithm                                                                                           |

| N_Probes            | Number of Probes in the NND algorithm                                                                                                   |

| NHA <sub>x</sub>    | NoC Hardware Address proposed in the thesis, where $x$ is an index reflecting the NAS number                                            |

| NIF                 | Network Interface                                                                                                                       |

| n <sub>period</sub> | The number of indices needed to have a period in the ACF-<br>based algorithm                                                            |

| NPKI                | The most recent running estimate of the noise peak in the Pan<br>Tompkins algorithm                                                     |

| Ντ                  | The specific number of index points on the x axis that are equivalent to have $\tau$ (period) on the x axis.                            |

| PEAKI               | PEAKI is the overall peak in the calculations of the Pan Tompkins algorithm                                                             |

| PROBE_PACKET_SIZE   | The size of the packet used for probing in the NND algorithm in the ENoP                                                                |

| Probe_Reply         | The parameter to detect if there was a reply from probing a NoC. It has a value of True or False.                                       |

| PS                  | The value of the PROBE_PACKET_SIZE in the the NND algorithm in the ENoP                                                                 |

| RANI                | Random non-zero Digit used for the NND algorithm                                                                                        |

| xxiv                |                                                                                                                                         |

| RR_AVERAGE      | The R-R measure in the Pan Tompkins algorithm                                                                                                                                                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RR_HIGH_LIMIT   | The high value of the RR measure based on RR_AVERAGE                                                                                                                                                                        |

| RR_LOW_LIMIT    | The low value of the RR measure based on RR_AVERAGE                                                                                                                                                                         |

| RR_MISSED_LIMIT | The missed value of the RR measure based on RR_AVERAGE.<br>After an RR MISSED LIMIT time has passed and no peaks<br>were detected, we implement the search-back technique using<br>T2 (the second threshold)                |

| RR'n            | The most recent R-R interval that fell between the acceptable<br>low and high RR-interval limits in RR_LOW_LIMIT,<br>RR_HIGH_LIMIT, and RR_MISSED_LIMIT.                                                                    |

| $RR_n$          | The most recent R-R interval in the R-R calculations in the Pan<br>Tompkins algorithm                                                                                                                                       |

| $R_y$           | Autocorrelation of the signal <i>y</i>                                                                                                                                                                                      |

| S(u, w)         | The STFT calculated for the Wavelet Theory, where $f(t)$ is the signal under study, $g(t)$ is the window function used to slice the signal and apply the Fourier Transform, $u$ is the time shift, and $w$ is the frequency |

| SPKI            | The most recent running estimate of the signal peak in the Pan<br>Tompkins algorithm                                                                                                                                        |

| synchronize(.)  | Function in the NND of ENoP responsible to fix the synchronization for communication between two NoCs                                                                                                                       |

| Т               | Period of a periodic function in seconds                                                                                                                                                                                    |

| t               | Time in seconds                                                                                                                                                                                                             |

| $t_0$           | The first sample time in the data chunk                                                                                                                                                                                     |

| $t_1$           | The time variable sample time in the data chunk                                                                                                                                                                             |

| <i>T1, T</i> 2  | Two adaptive thresholds (T1=2*T2) to select candidate QRS complexes in the Pan Tompkins algorithm                                                                                                                           |

XXV

| THRESHOLD11 | The first threshold applied in the Pan Tompkins algorithm                                     |

|-------------|-----------------------------------------------------------------------------------------------|

| THRESHOLD12 | The second threshold applied in the Pan Tompkins algorithm                                    |

| Time_Slot   | The variable that is used for TS.                                                             |

| TS          | The time of transmission, propagation, and processing of a probe message in the NND algorithm |

| и           | The time shift of the window in the Wavelet                                                   |

| W           | Frequency under study in the Wavelet                                                          |

| W(u, s)     | Wavelet Transform , where $s$ is the scale value                                              |

| x           | Index (variable) in the discrete function                                                     |

| X           | Random Signal                                                                                 |

| у           | Discrete signal used mainly for the ECG filtered signal in the equations                      |

| Z           | Variable of the filter in $H(z)$                                                              |

| $\Delta t$  | Difference between $t_1$ and $t_0$                                                            |

| ρ           | Index used in the equations                                                                   |

| τ           | Time period of a signal                                                                       |

| ψ           | The mother wavelet function                                                                   |

xxvi

### **Chapter 1**

#### Introduction

"There is nothing more difficult to take in hand, more perilous to conduct, or more uncertain in its success, than to take the lead in the introduction of a new order of things."

Niccolo Machiavelli (1469-1527 A.D.)

This chapter briefly introduces the problem we aim at solving and the motivation behind our goals. The main problem lies in analyzing one of the human heart signal-sets via the use of modern multicore technology instead of the nowadays used techniques that suffer from lack of accuracy and hinder the progress in heart diseases analyses. We also aim at founding a methodology that will foster and structure multicore HW/SW Codesign for Biomedical applications. The technology we adopt for the solution is the multiprocessor system-on-chip (MPSoC). MPSoC may also open new horizons to solving many problems (not only heart problems) that have been waiting for new technologies to evolve with new added values like quicker and finer analysis, parallelization, lower cost, flexibility, mobility, and lower power budgets. This chapter falls in three sections: section 1.1 describes my motivation that has been supported by my advisors, section 1.2 presents my contributions clearly, and section 1.3 introduces the organization of the remainder of this thesis.

#### 1.1. Motivation

Concerned about the changes occurring in the beginning of the 21<sup>st</sup> century and their effects on human life, I looked at some statistics from the World Health Organization (WHO) and studies made by many healthcare centers [188], and I was appalled by some figures and threats presented. More precisely, I choose a statement by Anthony Rodgers [189], from the Clinical Trials Research Unit at the University of Auckland in New

1

Zealand, to describe the main drive behind my motivation since his statement clearly describes the problem and the possibility to find preventable solutions as follows: